基于SoC FPGA进行工业设计及电机控制

● 磁场定向控制(FOC)。FOC是通过独立地确定和控制转矩和磁化电流分量来为电机提供最优电流的算法。在永磁同步电机(PMSM)中,转子已经磁化。因此,为电机提供的电流只用于转矩。FOC是计算密集型算法,但是美高森美电机控制参考设计已经针对器件资源的最优使用而构建。FOC算法包括Clarke、Park、逆Clarke和逆Park变换。

本文引用地址:http://www.eepw.com.cn/article/264457.htm● 角度估计。FOC的一个输入是转子角度。精确确定转子角度对于确保低功耗是必不可少的。增添确定位置和速度的物理传感器会增加系统的成本并降低可靠性。无传感器算法有助于消除传感器,但是增加了计算复杂性。美高森美针对无传感器控制提供了两个角度计算算法IP模块-一个基于Luenberger观测器,另一个基于直接反电动势计算。该公司还提供基于霍尔传感器和编码器的单独参考设计。

● PLL.PLL用于同步信号,在多个应用中有用,例如逆变器的角度估计和电网同步。

● 速率限制器。速率限制器模块可以实现系统变量或输入的平滑改变。例如,在电机控制系统中,如果电机所需的速度突然改变,系统可能变得不稳定。为了避免此类情形,速率限制器模块用于从初始速度转变到所需的速度。速率限制器模块可以进行配置以控制改变的速率。

● 空间矢量调制。空间矢量调制模块改善了直流总线利用率,并消除了晶体管开关的短脉冲。因为晶体管开启/关断时间比脉冲持续时间长,短脉冲会导致不正确的开关行为。

● 三相PWM生成。在所有计算的最后,可以得到三相电机电压。这些电压用于生成逆变器中晶体管的开关信号。PWM模块为六个(三个高侧和三个低侧)晶体管产生开关信号,并且具有死区时间和延迟时间插入等先进特性。可编程的死区时间插入特性有助于避免逆变器引脚上的灾难性短路情况。可编程的延迟时间插入特性使ADC测量与PWM信号生成能够同步。该模块可以配置成与仅由N-MOSFET组成的逆变器或同时包括N-MOSFET和P-MOSFET的逆变器一起工作。

(2)在SoC中调试FPGA设计。通常,在微控制器上调试设计比在FPGA上进行调试相对简单一些。在SoC中,可以利用FPGA的高性能,同时保持在微控制器中更快速调试的优势。美高森美SmartFusion2 SoC FPGA中的微控制器子系统和FPGA架构可以通过AMBA APB或AXI总线彼此进行通信。这样可以把测试数据注入FPGA架构中,或者从FPGA架构中记录调试数据,从而帮助实现运行时间的内部数据可视化,用于实时调试。固件代码可以单步运行,在代码中可以设置断点来分析FPGA寄存器数据。

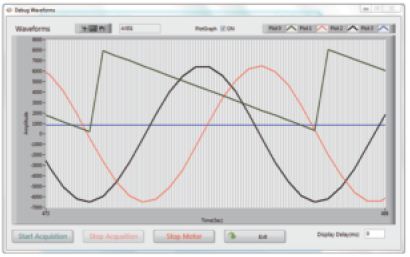

基于SmartFusion2 SoC FPGA的多轴电机控制解决方案通过USB连接至主机PC,并与图形用户界面(GUI)通信,进行启动/停止电机,设置电机速度值和其他系统参数,描绘多达四个系统变量,例如电机速度、电机电流和转子角度(图4)。

图4:GUI的屏幕截图-绘制内部参数:转子角度(绿色)、Valpha(红色)、Vbeta(黑色)、电机速度(蓝色)。

(3)生态系统。美高森美提供一组丰富的IP库,包括前面讨论过的数种电机控制功能。这些模块可以轻易定制,并可以在美高森美器件中移植。使用Libero SoC软件的Smart Design工具,这些模块可以采用图形方式配置和连接在一起。借助于这些IP模块,设计人员能够显着减少在FPGA中实现电机控制算法所需的时间。

这些IP模块已在以高达30,000r/min转速和200kHz开关频率运行的电机上进行了测试。

工业通信协议

工业网络的发展趋势是通过使用更快的网络通信替代点至点通信。实现此类高速通信需要支持更高的带宽,这对于同时处理电机控制算法的微控制器或DSP来说并不容易。在大多数情况下,会使用一个附加的微控制器或FPGA来处理与每个电机控制器的通信。通常使用的基于以太网的协议有PROFINET、EtherNet/IP和EtherCAT标准,这些标准仍然在演进。其他的协议包括了CAN和Modbus.在这种情况下使用SoC的优势,是在单一FPGA平台上支持多种工业以太网协议标准。

根据终端系统目标,可以通过重用IP和协议栈(用于通信)来优化系统的成本,或者通过仔细地在硬件(FPGA)和软件(ARMCortex-M3子系统)中划分功能来优化性能。

美高森美的SmartFusion2 FPGA具有内置CAN、高速USB和千兆以太网模块作为微控制器子系统的一部分。高速SERDES模块用于实现涉及串行数据传送的协议。

安全性

SmartFusion2 SoC FPGA器件具有数项设计和数据安全特性。DPA认证反篡改保护和加密特性等设计安全特性能够帮助保护客户的知识产权。SoC FPGA器件还包括数据安全特性,例如ECC硬件加速器、AES-128/256和SHA-256服务。对于数据安全性,可以使用EnforcIT IP Suite和CodeSEAL软件安全构件,EnforcIT IP包括一套可定制内核(作为网表),有效地将安全层移到硬件中。CodeSEAL将对策注入到固件中,可以独立地使用,或者用作EnforcIT的提升。

实现协议的灵活性可让设计人员使用多个安全层来认证从中央监控控制器进入的信息。

可靠性

在多个市场中安全标准的增长推动了高可靠性的需求,SmartFusion2经设计满足高可用性、安全关键型和任务关键型系统的需求,以下是SmartFusion2 SoC FPGA提供的某些可靠性特性。

(1)单粒子翻转(SEU)免疫零FIT率配置。高可靠性运作需要SEU免疫零FIT率FPGA配置,SmartFusion2架构具有不受α或中子辐射的免疫能力,因为它使用闪存来配置路由矩阵和逻辑模块中使用的晶体管。基于SRAM的FPGA在海平面上的FIT(时间失效)率可能为1k~4k,在高于海平面5,000英尺的位置会高得多。高可靠性应用可接受的FIT率低于20,这使得SmartFusion2最适合这些应用。

(2)EDAC保护。SmartFusion2器件具有错误检测与校正(EDAC)控制器,可防止在微控制器子系统(MSS)存储器中发生的单粒子翻转错误。

(3)无外部配置器件。在具有大量FPGA的复杂系统中,使用外部配置器件会降低可靠性。在上电时,FPGA需花费时间来进行配置,这在使用多个FPGA器件的应用中带来了设计复杂性。SmartFusion2 SoC FPGA在器件内部包含了配置存储器,它提供了在器件一上电时就开启的附加优势。

(4)军用温度级器件。SmartFusion2 SoC FPGA器件针对军用温度条件进行了全面测试。军用级器件具有10k和150k逻辑单元,并具有允许访问密码加速器的安全特性和数据安全特性。

总结

美高森美SmartFusion2 SoC FPGA使用经过高度优化的电机控制IP模块和经过验证的参考设计,提供了数种降低工业设计TCO的特性。从微控制器迁移的客户将能够重用某些旧代码,而FPGA设计人员将能够利用FPGA架构和ARM Cortex-M3子系统来创建一个高效的架构,允许电机控制模块和通信模块同时驻留在单一器件中。ARM Cortex-M3微控制器子系统的存在,可以实现灵活的设计和智能分区,而针对性能和成本做优化。微控制器子系统还可以在运行时间中注入和记录数据,加速调试FPGA设计。SmartFusion2平台还提供了实现工业通信协议的广泛选项。它同时提供用于设计和数据安全的多项安全特性,还提供了满足高可靠性需求的特性。SmartFusion2系列器件备有强大的生态系统支持,能够帮助客户以最低TCO来开发工业解决方案。

评论