功率分配系统(PDS)设计:利用旁路电容/去耦电容(一)

简介

FPGA设计人员在设计功率分配系统(PDS)时,面临着一个独特的任务。大多数其他大型、高密度IC(如大型微处理器)对旁路电容都有非常明确的要求。由于这些器件仅为执行其存储的特定任务而设计,所以其电源需求是固定的,仅在一定范围内有所波动。但FPGA不具备这种属性。FPGA可以不确定的频率、跨越多个时钟域,运行几乎无限多的应用,因此,预测其瞬态电流需求是一个非常复杂的过程。

由于无法确知一个新的FPGA设计的瞬态电流的变化情况,在设计第一个FPGA PDS时,唯一的选择就是采用保守的最坏情况设计法。

数字器件中的瞬态电流需求是产生接地反弹的原因,也是高速数字设计的死对头。在低噪声或高功率情况下,电源去耦网络必须根据这些瞬态电流需求准确地度身定制,否则,接地反弹和电源噪声将超出FPGA的限值。每种FPGA设计产生的瞬态电流不尽相同。本应用指南介绍了一种全面的设计方法,适用于满足特定FPGA设计的个别需要的旁路网络。

这个过程的第一步就是检查FPGA的利用率,大致了解其瞬态电流要求。

接下来,保守地设计一个满足这些要求的去耦网络。第三步,通过模拟和修正电容数量和额定值,精细调整这个去耦网络。第四步,完成全部设计;第五步,测量设计。测量包括利用示波器和频谱分析仪检测电源噪声。取决于测得结果,可能有必要再次重复元件选择和模拟步骤,以优化这个针对特定应用的PDS。第六步是可选步骤,适用于要求完美的PDS的情况。

去耦网络基本原理

在开始进入PDS设计流程之前,必须理解所涉及的基本电气原理。这部分讨论了PDS的用途及其组件的属性。此外,还介绍了独立式电容的布局和贴装等重要方面,以及关于PCB的几何形状和叠层的建议。

PDS旨在向一个系统中的各种器件提供电源。系统中的每个器件不仅各有适于其运行的电源要求,而且对该电源的噪声也有特定要求。大多数电子器件,包括所有的Xilinx FPGA,均有一个适用于所有电源的要求,即VCC上下波动的幅度不得超过VCC额定值的5%。在本文档中,VCC通常是指FPGA的所有电源:VCCINT、 VCCO、VCCAUX和VREF。本文未涉及千兆位级收发器(MGT)模拟电源(AVCCAUXTX、AVCCAUXRX、VTTX、VTRX)。关于这些电源的特定说明,请参阅《RocketIO™收发器用户指南》(参考书目#1)。

这个要求规定了最高电源噪声,通常称为“波纹电压”。如果器件的电源要求为VCC不得超过额定值的±5%,就表示,峰间波纹电压不得超过额定VCC的10%。这个结论假设额定VCC就是技术规格表中给出的额定值。如果不是,那么就必须将VRIPPLE调节至额定值10%以内的相应值。

数字器件的功耗会随时间的推移而变化,变化频率范围广泛。功耗的低频率变化通常是在启用或禁用器件和器件的较大部分时发生。发生这种情况的时间标度可以从数毫秒到几天。功耗的高频率变化则是器件内部独立元件的切换动作引起的,这种变化取决于时钟频率的标度以及时钟频率最初的谐波。

由于一个器件的VCC电压水平是固定的,所以变化的电源需求将表现为变化的电流需求。PDS必须适应这种电流消耗的变化,并且尽可能减少电源电压的变化。

当器件的电流消耗发生变化时,功率分配系统不能立即对变化做出响应。在PDS响应之前的短时间内,该器件的电源电压将发生变化,从而产生电源噪声。PDS响应延迟的主要原因有两个,分别对应于PDS的两个主要元件。

PDS的第一个主要元件是稳压器。稳压器负责检测PDS的输出电压并调节输出的电流量,以保持电压恒定。大多数常见的稳压器都在数毫秒到数微秒之间完成这种调节。对于各种频率的变化,从直流到几百千赫,稳压器在保持输出电压稳定性方面非常有效(取决于稳压器)。对于频率超出这个范围的所有瞬态事件,在稳压器响应新的电源需求之前,存在一段时滞。例如,如果器件的电流需求在几毫微秒之间突然增加了,那么,在稳压器调节至器件需要的新的、更高电流之前,该器件的电压将有所下降。这段延迟的时间从数微秒到数毫秒之间不定,这个过程中,电压将降低。

PDS的第二个主要元件是旁路电容或去耦电容。在本应用指南中,“旁路”和“去耦”两个词可以互换。这种元件的功能是作为器件的本地能源存储器。这种元件不能提供直流电源,因为它们只能存储少量电能(稳压器的作用是提供直流电源)。这个本地能源存储器的功能是以极快的速度响应变化的电流需求。在从数百千赫到数百兆赫的频率范围内,电容可以在几毫秒到毫微秒之间,有效地保持电源电压。对于超出这个范围的变化,去耦电容则无能为力。例如,如果器件的电流需求在几微微秒内突然提高,那么,在电容能够向器件提供额外电量之前,该器件的电压将有所下降。如果器件的电流需求改变了,并在数毫秒内保持新的水平,那么,与旁路电容并行运行的稳压电路将有效地接替这些电容,并调节自己的输出电压,满足新的电流需求。

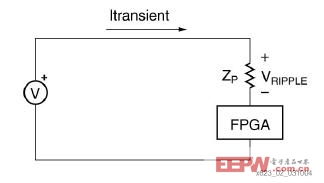

图1显示了PDS的主要元件:电源、去耦电容和接通电源正在运行的器件(在本例中,是一个FPGA芯片)。

|

图1:简化的PDS电路图 本文引用地址:http://www.eepw.com.cn/article/258864.htm |

|

图2:更加简化的PDS电路图 |

电感的作用是什么?

电容和PCB电流通道的属性之一就是延迟电流变化。因此,电容不能立即响应瞬态电流,或者高于其有效频率范围的变化。这种属性称为电感。

可以将电感视作电荷的动量。其中,电荷在导体中以一定速率移动,代表一定量的电流。如果电流水平发生变化,那么,电荷就必须以不同的速率移动。由于该电荷有一定的动量(保存的磁场能量),因此,要在一段时间后电荷才能实现减速或加速。电感越强,对改变的阻力就越强,从而使得电流需要更长时间才能发生变化。

PDS的目的是满足器件可能有的任何电流需求,并尽可能迅速地响应这种电流需求的变化。如果未能满足这种电流需求,那么,器件的电源电压就会发生变化。这就是电源噪声。由于电感会阻碍旁路电容迅速响应变化的电流需求的能力,所以应当最大限度地降低电感。

图1显示了FPGA和电容之间的电感和电容和稳压器之间的电感。这种电感是电容自身以及PCB中的所有电流通道的寄生现象。必须最大限度地降低所有这些电感。

电容寄生电感

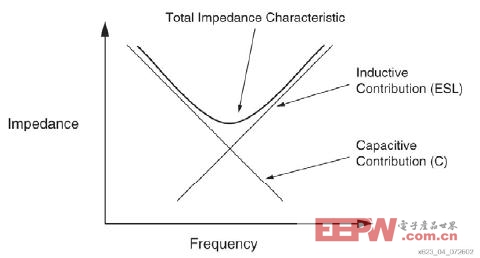

在电容的各种属性中,通常认为电容值是最重要的。然而,在PCB PDS设计领域,寄生电感属性(ESL,即等效串联电感)与电容值同样重要,甚或更为重要。

影响寄生电感的一个重要因素是封装的尺寸。一般而言,极为简单、体积小巧的电容的寄生电感低于体积较大的电容。就像较短的电线产生的电感低于较长的电线,较短的电容产生的电感也低于较长的电容。同样地,就像较粗或较宽的电线产生的电感低于较细的电线,较粗的电容产生的电感也低于较细的电容。

由于这些原因,在选择去耦电容时,应当选择特定额定值中体积最小的封装。类似地,对于特定封装尺寸(尤其是固定的电感值),应当选择采用该封装的电容中电容值最高的。

表面安装式芯片电容是目前市场中体积最小的电容,因此,是分立式旁路电容的理想选择。对于低于2.2 μF的极小的电容值,如0.001 μF,通常使用X7R或X5R型电容。这些电容具备很低的寄生电感和可接受的温度特性。对于较高的电容值,如1000 μF,则使用钽电容。这种电容具备较低的寄生电感和相对较高的等效串联电阻(ESR),使其具备较低的品质因素,从而能够提供范围广泛的有效频率。钽电容不仅具备相当高的电容值,而且封装尺寸也不大,从而降低了板上空间占用。如果没有钽电容可用,可以使用低电感电解电容。具备类似特性的其他新技术也可使用。

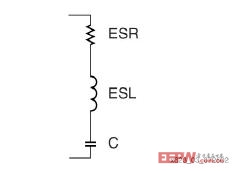

真正的电容具备多种特性,包括电容值、电感以及电阻。图3显示了一个真正的电容的寄生模式。应当将一个真正的电容视作一个RLC电路。

|

图3:真正的、而不是理想的电容的寄生现象 |

|

| 图4:寄生效应对总阻抗特性的贡献 |

评论