Giga ADC 介绍及杂散分析(下)

3.4杂散信号的优化

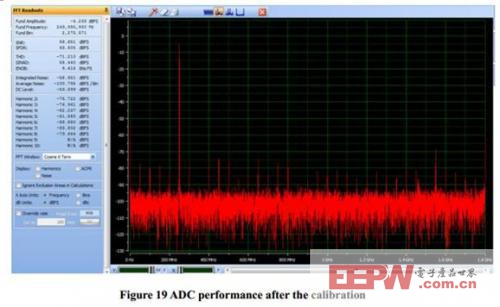

为了达到最佳的输出杂散性能,在Giga ADC,主要采用了校准环路,来优化输入电路的偏置误差、增益误差。如下图所示,在校准前后,ADC的性能可以优化10dBc以上。

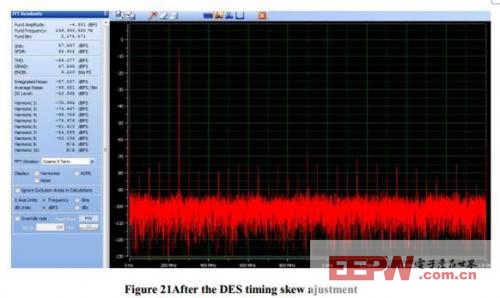

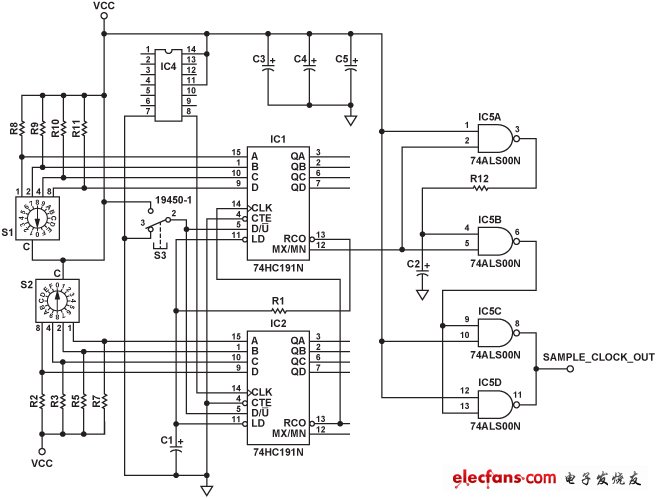

同时,当Giga ADC工作在DES mode,两路采样时钟间的skew对于Fs/2- fin的杂散非常重要;芯片提供了两路采样时钟的skew调整功能,可以通过寄存器的配置来降低Fs/2 - fin的杂散,如下图所示。

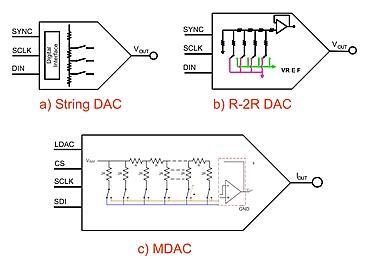

除此之外,ADC的外部输入电路设计也需要尽量优化,确保两路差分电路的平衡一致,阻抗的匹配。Giga ADC提供了DESI,DESQ,DESIQ,DESCLKIQ等几种DES模式下输入结构;综合输入平坦度,插入损耗和最终的ADC性能测试结果,DESIQ模式的性能最佳,并且推荐采用多层Balun和以下的输入电路。

4、结论

本文主要介绍了TI Giga ADC采用的架构,通过这一先进的架构,TI实现了业界最高采样率的12bit/10bit ADC,并被广泛使用到了卫星、雷达、微波等通信领域。同时本文也分析介绍了Giga ADC中的输出杂散的形成原因,以及相应的优化措施。

5、参考资料

[1] ADC08D1520 Datasheet

[2] Explicit Analysis of Channel Mismatch Effects in Time-Interleaved ADC Systems, Naoki Kurosawa, etc. 2001, IEEE

[3] A 1.8-V 1.6-GSample/s 8-b Self-Calibrating Folding ADC With 7.26 ENOB at Nyquist Frequency, Robert C. Taft, etc. 2004, IEEE

Giga ADC 介绍及杂散分析(上)

评论