视频综合集控系统的低功耗设计原则

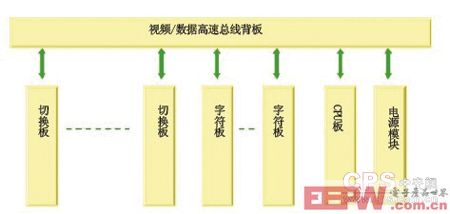

以当前比较先进的MSIP通用化模块结构技术为例,其核心设计思想是将视频输入输出、音频输入输出、中文字符叠加、全交叉切换管理、光接收发射、报警输入输出、网络视频编解码等各功能模块按照标准协议统一硬件接口和底层协议栈,通过标准机架式机箱的内嵌式导轨卡槽组装到通用高速总线背板上。各种功能模块根据统一的标准属性类别编码,能够依照实际需求灵活搭配,内置到通用总线背板的任意插槽,板卡数量位置无须地址限定,系统自动扫描识别后快速上线运行,日后客户可自行扩展升级维护各类功能模块,系统部署成本降低至少20%。比如基于此平台开发的VMS视频综合集控平台系统,采用7U标准插卡式机箱,CPU单元、码分器、网络交换机、电源模块全部内置,支持256路模拟视频输入64路模拟视频输出,支持多路网络视频编解码模块,支持数字视频输入输出,实现模拟数字视频信号的混合切换控制,用户在网络内任意节点即可远程浏览控制前端图像场景,还可内置多个32路报警信号输入模块或者网络报警主机,实现对周界报警探测器各种报警类型的支持(图2所示)。

模拟视频、数字视频都可通过采用接口标准相同的编解码模块实现统一规范,即插即用,解决多种视频制式兼容的问题。而对视频图像进行综合管理的软件单元也需要模块化设计,用户可以根据系统的实际需求对CMS总控管理、录像存储、用户权限、代理转发、WEB服务、报警管理、GIS地图等各软件单元进行菜单式配置,既可以独立部署,也能够协同工作。

多模块集成的主要作用就在于能够实现与声音图像的综合联动,比如周界报警探测器触发报警后关联预设的一路或多路视频切换显示和录像存储,音频信号超过设定分贝阈值后关联预设的视频切换显示,视频场景感知设定区域有物体移动后关联预设的视频切换显示,如果前端摄像机是云台变焦摄像机,则会启动预设的预置位和巡航轨迹。对于这类综合联动的智能预设处理,可以借助宏指令实现快捷编辑和自定义调用。宏是一个用户自定义的操作指令,以替代人工进行的一系列费时而难以记忆的重复性键盘操作,自动完成预设的各种操作,提供对紧急事态的应急预案处理。通过宏这个友好的人机交互界面,将需求输入,就可以让系统自动实现对各个扩展功能模块的统一调用和关联操作,用户无需关心底层的硬件设备如何实现指令互通和数据交换。究其根本就在于所有功能模块均采用了统一的协议栈和标准的接口设计,从而组成高度智能的一体化集成设备。

3、统一平台应用,平滑演进

面对设备众多复杂的大型视频监控系统,管理环节中最低效的是不能进行快捷有效地操作。为此,需要从统一平台应用接口和强化单类产品事件流管理两方面入手。

统一平台应用接口要求所有软件单元和硬件模块都通过一台总控服务器管理,统一数据交换、统一时钟、统一视频传输,共享处理资源。以VMS视频综合集控平台系统为例,通过这台总控服务器可以实现对系统内所有的基准功能模块和扩展功能模块的管理,包括对视频输入输出、存储磁盘、录像通道、用户权限、事件触发、操作日志的全部设置,用户通过客户端只需要访问到这个IP即可,不但节省了网络资源,而且提高了执行效率。

事件流管理则将单核中枢向多核节点推进,核心思想是将相对庞大的视频综合集控平台系统分解为二三级的子设备,从而便于中小系统的低成本快速部署。比如智能网络矩阵通过WEB集控技术,以音视频信息流为数据参照主线,绑定网络视频输入输出、报警输入联动、报警分区控制、用户权限管理、前端操作级别等功能,将多业务模块一体化集成,用户通过IE浏览器便捷管理,无需专用工作站服务器,也无需复杂连接和繁琐调试,基于标准协议接口的网络键盘也为用户提供了方便灵活的人机交互界面。

4、低功耗,高能效

不论是高密度紧凑结构设计,还是模块化接口通用高速总线,都需要在系统设计和产品设计中考虑采用多种创新技术手段、使用更高主频、更高性能、更小封装体积的芯片处理方案。在众多的复杂系统设计中,FPGA是一种较好的选择,可以帮助设计人员提高系统易用性扩展性、提高单位密度。比如在视频切换和字符叠加电路中,原先的通用方案需要配置多路芯片,致使电路复杂,PCB电路板面积增加,系统集成度下降。通过FPGA可以自动识别视频制式并产生同步信号实现视频同步无抖切换,而且可以同时用户自定义字符图形叠加到多路视频信号中,执行效率和能耗压缩率提高了8倍。比如目前最新上市的S系列32入16出视频矩阵,机箱仅有1U高度,采用了多核单板式平台技术,切换、控制、交换、叠加全部由一枚主芯片解决,为紧凑型小系统提供了最优选择。

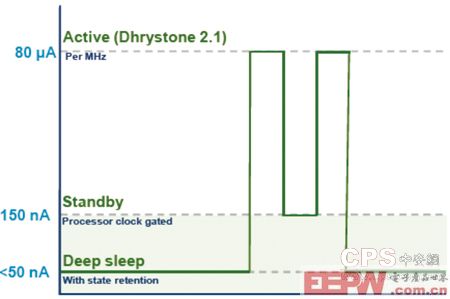

功耗是一笔较大的综合成本开支,因为要处理过多的功耗所造成的热问题时,电路板设计的复杂性增加了,对端口的密度和带宽的要求上升了,但是波形因数下降了,迫使开发工程师对项目进度和预算做出调整。(图3所示)

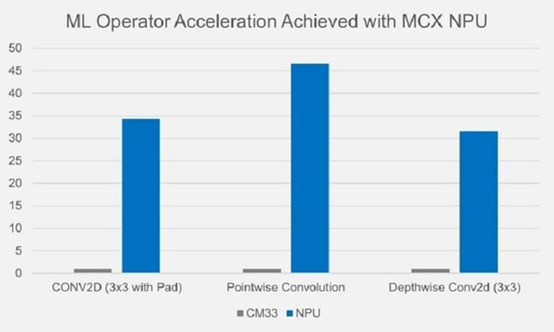

芯片能耗包括多方面,比如FPGA的功耗就来自于预编程静态器件功耗、浪涌编程电流、编程后的静态功耗、动态功耗。为解决此问题;一方面利用更小芯片制程工艺比如65nm可以解决这些问题,另一方面深入挖掘节能潜力,利用多种节电技术降低整机功耗,比如采用低耗高效能的DSP和PCB、采用智能软件节电技术、功率控制技术(图4所示)。

评论