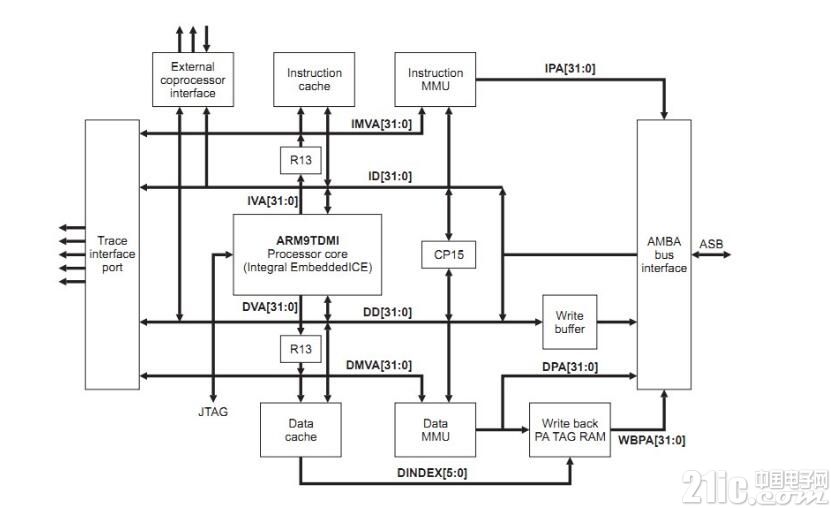

32位嵌入式CPU中系统控制协处理器的设计与实现

电路的定制设计主要指的是,在Composer环境中手工设计晶体管级的电路。电路参数的确定由Synopsys的电路仿真工具Hspice协助完成。将从设计好的电路中抽出的网表输入到Hspice中,仿真计算出电路的时延

为了减少全定制设计的工作量,电路设计要建立模块的微体系结构。其中CP0的基本单元确定如下:基本的CP0寄存器(时钟上沿同步寄存器) ;32位比较器;32位加法器;多选一选择器(包括2选1、3选1和4选1 MUX);驱动器(即反相器;其尺寸参数化以适应不同驱动要求)。

加法器基本采用了超前进位加法器的思想,然后在整体上分成两个16位加法器的模块,模块间采用进位选择加法器的思想,从而大大提高了整个电路的速度。但其面积比全部采用超前进位加法器时要大20%左右。

设计出来的电路逻辑是否正确,时延是否满足要求,分别需要做功能验证和电路仿真。在验证了各个小模块的正确性之后,需验证小模块之间的逻辑连接正确性,最后对整个模块进行验证,进一步分析电路找出模块中的最长路径,通过仿真、更改电路、再仿真的过程,来确定该模块是否能达到预期的逻辑设计要求。

版图的全定制设计

版图设计是根据电路功能和性能的要求以及工艺条件的限制(如线宽、间距、制版设备所允许的基本图形等),设计集成电路制造过程中必需的光刻掩膜版图。版图设计与集成电路制造工艺技术紧密相连,是集成电路设计的最终目标。

在设计过程中,为了降低设计的复杂度,采用混合设计模式,即全定制和标准单元设计相结合的设计方法。这样既有利于保证电性能的要求,又能减小设计周期,是一种较为理想的设计模式。

在全定制版图中,设计过程分为两步完成,每个大单元电路总是由各种基本电路组合而成,所以第一步是绘制基本电路的版图,画完后做DRC和LVS,保证基本电路的正确性。第二步用这些基本电路来组合成大的单元。

全定制芯片设计可以根据数据通路电路的规则手工设计出合理的版图。版图设计中尽量保证各个部分的规整和对称,使其易于扩展。版图的布局中使联系较多的单元尽量靠近,从而缩短互连线的长度,减小每个单元的面积和时延,降低器件的负载电容,采取的具体措施如下:

1) 增加地与衬底、电源与阱的接触,在没有器件和走线的空白处多打接触孔,并且将其与电源或地连接,有利于收集噪声电流、稳定电位、减小干扰和被干扰;

2) 形成网状的电源地线网络;

3) 避免同层或上下两层中长金属线的平行走线,对噪声敏感的线尽量布得短;

4) 避免首尾循环的走线;

5) 在满足设计规则的前提下,尽量减小MOS管的有源区面积,以减小寄生电容,提高工作速度;

6) 在数据通路设计中,要为金属连线留下一些备用位置。

控制通路与数据通路的集成设计及验证

逻辑层次

控制部分直接用行为级的RTL代码,数据通路部分由从全定制电路导出的结构化RTL代码,得到全模块的逻辑描述。

可采用向量进行验证,与采用RTL(或C模型)进行验证的结果(trace文件)进行比对。

电路层次

电路层次控制通路与数据通路的集成可以借助Composer顺利完成。

对于延时信息的获取,数据通路或控制通路内部的路径分别采用Hspice仿真及综合来获得,分析内部是否存在关键路径。

涉及数据通路与控制通路之间的关键路径,可以由全定制部分提交数据通路部分接口的输入/输出时延信息,即该路径在其内部需要的时间。以这些信息作为外部约束,再对相关模块进行综合(按模块综合),结果文件中将得到集成后的关键路径。

版图层次

要保证版图与电路的一致性,需要做LVS验证。即将控制通路的门级网表导入Composer,与数据通路的全定制电路合成总电路,并由此提取电路级的Spice网表进行LVS验证。LVS采用的工具为Mentor Graphics 的Calibre工具。

结语

本文主要研究了基于MIPS 4Kc体系结构的系统控制协处理器的设计和实现,包括精确异常处理的实现方式和全定制的物理设计。在对精确异常处理机制的过程中通过增加写使能判别逻辑达到了缩减关键路径时延的目的,降低了控制逻辑的复杂性,同时增加了全芯片的可靠性。本文的设计通过了逻辑、电路验证,应用于32位CPU的设计中,并采用中芯国际的1P6M 0.18mm工艺成功流片。

评论