锁相倍频电路的实现

2.2 锁相倍频电路

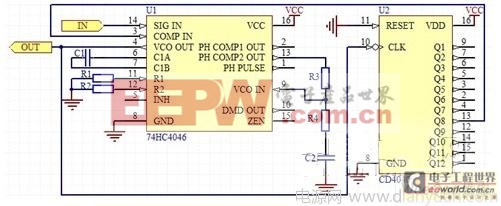

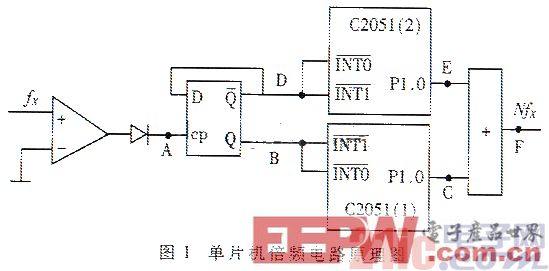

此锁相倍频电路采用了一片锁相环芯片74HC4046、一片累加计数器CD4040和低通滤波器,其电路连接图如图3所示。

图3 锁相倍频电路原理图

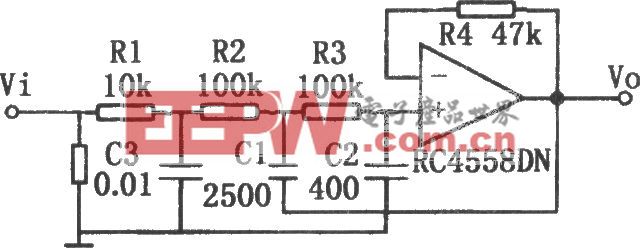

A相电压经过零信号检测电路后得到与A相电压同步的50Hz方波,作为锁相倍频电路的输入信号进入锁相环芯片74HC4046的14号引脚,4 号引脚是74HC4046内部压控振荡器的输出端,其输出信号输入CD4040的10号引脚,进行256倍的倍频,其倍频信号从二进制计数器CD4040 的13号引脚输出又进入74HC4046的3号引脚,即比较信号输入端,74HC4046内部的相位比较器对两个信号进行相位比较后,从相位比较器Ⅱ的输出端13号引脚输入,经过由 、 和组成的低通滤波器,将高频噪声滤除后,再进入74HC4046的内部压控振荡器,作为其控制信号,从上述过程可以看到这是一个闭环控制系统,经过不断的调节,使输出信号频率为输入信号频率的256倍,并且使输入信号与比较信号的频差为零。

3 实验结果及分析

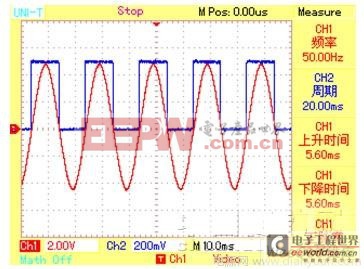

过零检测电路在外加信号频率为50Hz正弦波时的实验波形图如图4所示。

图4 过零信号与正弦波形

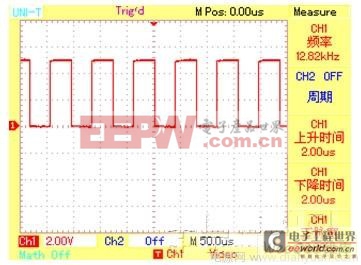

图5所示为所设计的锁相倍频电路的输出实验波形。

图5 锁相倍频电路输出的12.82kHz方波

压控振荡器的输入电压来自于低通滤波器的输出,所以输出频率会有一定的波动,此锁相倍频电路的输出频率范围在12.77kHz- 12.82kHz。锁相倍频电路输出的频率在被DSP捕捉到后就会启动AD7656对信号采样,由于输出频率的脉动,采样点的正弦和余弦值可能会与表中存储的正弦和余弦表有一定误差。在满足锁相速度的前提下,应当尽可能减小低通滤波器的截止频率,以减小输出频率的波动。

比较器相关文章:比较器工作原理

低通滤波器相关文章:低通滤波器原理

分频器相关文章:分频器原理 鉴相器相关文章:鉴相器原理

评论