一种基于FPGA的电子稳像系统的研究与设计

1 系统涉及的关键技术

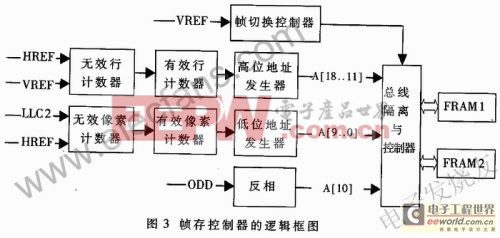

摄像头输入的PAL制式电视信号首先通过视频处理接口完成对其解码、同步和数字化的工作,数字化后的图像信息进入到由FPGA实现的帧存控制器中,完成数据的交换(数据的缓冲),同时完成系统要求的去隔行和放大的操作,最后处理好的数据通过VGA控制器,完成时序变化,经视频、A变为模拟信号送到VGA监视器上实时显示。

1.1 视频处理接口

由于在进行视频处理时,多为从摄像头输入模拟信号,如NTSC或PAL制式电视信号,除图像信号外,还包括行同步信号、行消隐信号、场同步信号、场消隐信号以及槽脉冲信号等。因而对视频信号进行A/D转换的电路也非常复杂。Philips公司将这些转换电路集成到了一块芯片中,从而生产出功能强大的视频输入处理芯片SAA7111,为视频信号的数字化应用提供了极大的方便。

系统设计采用SAA7111对复合信号进行采样、同步产生、亮色分离并输出标准的数字化信号。SAA7111输出的数字化图像信息符合CCIR.601建议,PAL制式的模拟信号数字化后的图像分辨率为720×572,像素时钟13.5MHz。在本稳像系统中要求图像输出符合VGA(640×480,60Hz)标准,因此在采集数据时要对数据进行选择,避开行、场消隐信号和部分有效像素信息,在较大的图像中截取所需要的大小。SAA7111向帧存控制电路输出像素时钟(LCC2)、水平参数(HREF)、垂直参考(VREF)、奇偶场标志信号(ODD)和16位像素信息(RGB565).其中LCC2用来同步整个采集系统;HREF高电平有效,对应一行720个有效像素;VREF高电平有效,对应一场信号中的286个有效行;ODD=1时,标志当前场为奇数场;ODD=0时,标志当前场为偶数场。采用16位RGB表示每个像素的彩色信息。图1(a)为数字化图像中的一行像素的时序图。其中两个HREF分别表示有效行的起始与结束位置,实际为一个信号;可以清楚地看到一行中有效的720个像素与像素时钟LLC2的对应关系,在采集时通过帧存器控制电路选择其中部的640个像素进行采集。图1(b)为一帧数字图像的输出时序图。可以看到在第624~22行时,VREF处于无效状态,因此在后续的采集中,这部分的信息不予处理并通过ODD的电平区分奇偶场数据。

p2p机相关文章:p2p原理

评论