信号完整性分析基础系列之关于眼图测量(上)

眼图的历史可以追溯到大约47年前。在力科于2002年发明基于连续比特位的方法来测量眼图之前,1962年-2002的40年间,眼图的测量是基于采样示波器的传统方法。

在长期的培训和技术支持工作中,我们发现很少有工程师能完整地准确地理解眼图的测量原理。很多工程师们往往满足于各种标准权威机构提供的测量向导,Step by Step,满足于用“万能”的Sigtest软件测量出来的眼图给出的Pass or Fail结论。这种对于Sigtest的迷恋甚至使有些工程师忘记了眼图是可以作为一项重要的调试工具的。

在我2004年来力科面试前,我也从来没有听说过眼图。 那天面试时,老板反复强调力科在眼图测量方面的优势,但我不知所云。 之后我Google“眼图”,看到网络上有限的几篇文章,但仍不知所云。刚刚我再次Google“眼图”,仍然没有找到哪怕一篇文章讲透了眼图测量。

网络上搜到的关于眼图的文字,出现频率最多的如下,表达得似乎非常地专业,但却在拒绝我们的阅读兴趣。

“在实际数字互连系统中,完全消除码间串扰是十分困难的,而码间串扰对误码率的影响目前尚无法找到数学上便于处理的统计规律,还不能进行准确计算。为了衡量基带传输系统的性能优劣,在实验室中,通常用示波器观察接收信号波形的方法来分析码间串扰和噪声对系统性能的影响,这就是眼图分析法。

如果将输入波形输入示波器的Y轴,并且当示波器的水平扫描周期和码元定时同步时,适当调整相位,使波形的中心对准取样时刻,在示波器上显示的图形很象人的眼睛,因此被称为眼图(Eye Map)。

二进制信号传输时的眼图只有一只“眼睛”,当传输三元码时,会显示两只“眼睛”。眼图是由各段码元波形叠加而成的,眼图中央的垂直线表示最佳抽样时刻,位于两峰值中间的水平线是判决门限电平。

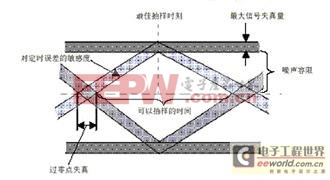

在无码间串扰和噪声的理想情况下,波形无失真,每个码元将重叠在一起,最终在示波器上看到的是迹线又细又清晰的“眼睛”,“眼”开启得最大。当有码间串扰时,波形失真,码元不完全重合,眼图的迹线就会不清晰,引起“眼”部分闭合。若再加上噪声的影响,则使眼图的线条变得模糊,“眼”开启得小了,因此,“眼”张开的大小表示了失真的程度,反映了码间串扰的强弱。由此可知,眼图能直观地表明码间串扰和噪声的影响,可评价一个基带传输系统性能的优劣。另外也可以用此图形对接收滤波器的特性加以调整,以减小码间串扰和改善系统的传输性能。 通常眼图可以用下图所示的图形来描述,由此图可以看出:

(1)眼图张开的宽度决定了接收波形可以不受串扰影响而抽样再生的时间间隔。显然,最佳抽样时刻应选在眼睛张开最大的时刻。

(2)眼图斜边的斜率,表示系统对定时抖动(或误差)的灵敏度,斜率越大,系统对定时抖动越敏感。

图一 眼图

(3)眼图左(右)角阴影部分的水平宽度表示信号零点的变化范围,称为零点失真量,在许多接收设备中,定时信息是由信号零点位置来提取的,对于这种设备零点失真量很重要。

(4)在抽样时刻,阴影区的垂直宽度表示最大信号失真量。

(5)在抽样时刻上、下两阴影区间隔的一半是最小噪声容限,噪声瞬时值超过它就有可能发生错误判决。

(6)横轴对应判决门限电平。 ”

是该专门写篇文章详细讲解眼图了!写得不正确、不到位的地方,恳请大家指正,以使这篇文章将能不断修改完善,有益于广大工程师们的学习。

一、串行数据的背景知识

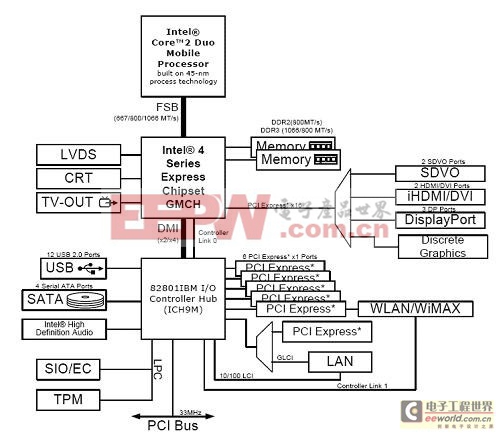

串行信号种类繁多,在图二所示的有PCI Express,Rapid IO,DVI,S-ATA,USB,SDH,XAUI,等,其实现在的流行总线还远不止这些。每年都出来一些新流行的串行总线。每些总线差不多都有一个权威机构来定义该总线的信号标准和测试规范,这些机构成员多是由来自于不同公司的专家兼职担任。当然,关于PC的串行总线差不多由Intel来领导。图三所示某基于Intel Chipset的笔记本电脑的框架图中的各种总线,除了DDR和FSB是并行数据之外,其它都是串行数据了。这些权威机构除了定义规范,当然也会有一些利益博弈。所以有新的利益集团(这是一个中性的词)策划推广的时候就可能有新的总线规范出台,这就象3G有三种标准一样。 你方唱罢我登场,搞得下游厂商手忙脚乱。

串行数据总线越来越多,权威机构定义的测试规范也纷繁芜杂,我一直觉得该将这么多的权威机构统一为一个权威机构,就叫“串行总线国际工程师协会”好了,如果力科最先发起并领导这个协会,然后定义一系列的串行信号测试规范中都只推荐力科示波器,那么亲爱的朋友们,这个Day Dream的最终结果是什么? 示波器行业也许会重新大洗牌。人们总相信权威机构推荐的,譬如我们平时用牙膏等都会相信“中华医学会”之类的推荐.

信号速率不断加倍再加倍,2004年我刚到力科的时候,主流的串行信号速率在PC行业是2.5Gb/s,在通信行业是3.125Gb/s,如今,PC行业已Double到5Gb/s,通信行业已Double到6.25Gb/s,而且PC行业的8Gb/s,通信行业的12.5Gb/s似乎已指日可待。速率越来越高,并行数据必然要让位于串行数据。串行数据传输的典型结构框图如图三所示,“万变不离其宗” ,都是“两根差分线”。相比于并行数据,串行数据的优点是:1,信号线的数量减少。2,消除了并行数据之间传输的延迟问题。

图二 串行数据的整体特点

图三 某笔记本电脑架构示意图

3,因为时钟是嵌入到数据中的,数据和时钟之间的传输延迟也同样消除了。

4, 传输线的PCB设计也更容易些。

5, 信号完整性测试也更容易。

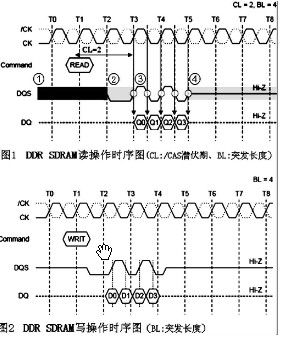

图四 串行信号实例

串行数据的测试点包括了芯片的发送端和接收端等不同节点。描述串行数据的常用单位是波特率和UI,譬如3.125Gb/s表示为每秒传送的数据比特位是3.125G比特(byte),对应的一个单位间隔(1UI)表示为一个比特位的宽度是波特率的倒数,1UI=1/(3.125Gb/s)=320ps。现在比较常见的串行信号码形是NRZ码。正电平表示”1”,负电平表示“0”。图三所示是示波器捕获到的一组串行信号,虚线之间的时间间隔代表了一个

评论