自适应计算在机器人领域的应用

序言

2021年 4 月, 赛灵思创新性地推出自适应系统模块(SOM)产品组合 Kria SOM。作为一种量产型小尺寸嵌入式板卡,该平台经济实惠、开箱即用,最主要是赛里思通过工具创新,借助SOM赋能上百万软件开发者,使其可以获益于赛灵思自适应计算平台的高性能和灵活性优势,而且可以使其将应用部署时间缩短多达 9 个月。

“一石激起千层浪”, Kria 的出现,在其所面向的广泛的边缘应用领域引起积极的反响,而机器人应用就是其中之一。

传统的机器人软件开发,是基于预定义的架构和约束条件在给定机器人 CPU 中进行功能编程。然而采用自适应计算后,构建机器人行为则是在进行架构编程。通过采用自适应计算,机器人专家能在运行中适配机器人计算系统的一个或多个属性(如它的确定性、功耗、安全态势或吞吐量)。

然而,机器人专家并不是硬件工程师,他们普遍缺乏与嵌入式技术相关的专业知识。本文将从当今热门的 "自适应机器人"概念入手,从 ROS 2 机器人专家的视角介绍自适应计算,并提出一种能够让 FPGA 在 ROS 2 生态系统中起主要作用的架构。这个架构适用于多种平台和多种技术,并且便于移植。架构的核心组件在 Apache 2.0 许可证下提供,为机器人专家充分运用自适应计算,实现软件定义硬件铺平了道路。

其中 :

● “连载一:什么是自适应机器人”通过三大基本特征,征剖析自适应机器人的概念产生、发展及特点

● “连载二:工业类比CPU/GPU,ASIC和FPGA,谁更适合机器人计算”通过工业车间操作流程进行类比,形象展示不同处理器平台对于机器人系统的权衡利弊

● “连载三:为什么 FPGA 能在机器人中起到重要作用” 介绍机器人自适应计算的概念,对自适应计算的核心技术与功能进行总体介绍,并详解 FPGA 在机器人应用中发挥的作用,以及有关软件定义硬件的概念

● “连载四:如何理解面向机器人的“软件定义硬件””通过比较传统机器人软件编程和基于赛灵思自适应解决方案平台的编程模式进行比较,介绍软件定义硬件的实现方法

● “连载五:为什么是通过 ROS 2集成自适应计算?”简要介绍 ROS 2 及其与自适应计算的渊源

● “连载六:自适应计算平台实现 ROS 之路”则分享了前期业界在自适应计算及在机器人操作系统上的相关研究。

● “连载七:用ROS 2 在机器人内部集成自适应计算的新架构”介绍了本文提出的架构,以及如何利用这个架构为 ROS 2 集成自适应计算功能,并使其发挥重要作用。

机器人专家花费大量时间,以计算图形式构建机器人行为,解决手里的机器人任务。他们经常使用现代的 C++ 语言,通过高级软件工程操作,构建复杂的实时系统。然而,他们并不是硬件工程师。机器人专家普遍缺乏硬件和嵌入式技术专业知识,因而妨碍了 FPGA 等自适应计算技术的广泛采用。本文在既往研究的启发下,介绍机器人自适应计算的基础知识,并提出一种生成 ROS 2 软件定义硬件的架构。与过去的其他方法相比,本文提出的方法是假设面向的是没有硬件或嵌入式技术专业知识的机器人专家,是以机器人专家为中心的角度提出的。

本文首先总结了开发机器人时选择正确计算平台的重要性,以及机器人内部软硬件之间的重要关系。然后使用工厂做类比,简要讲解 CPU、GPU、FPGA 和 ASIC 的计算原理并回顾相关研究文献,发现 FPGA 因低功耗、高性能、确定性、可重配置能力、安全性和自适应特征,在用于机器人时具有显著的优势。此外,本文也回顾了有关将 ROS 集成到 FPGA 平台的既往研究,发现这些研究都从硬件工程师的角度出发,导致做出的设计决策往往严重制约性能空间。出于这个原因,本文从ROS 2 机器人专家的视角提出了一个提出建议,即全面考虑 ROS 2 的硬件加速。这一视角能体现:a) 优化流程中、流程内、网络内(含底层)的 ROS 2 计算图交互;以及 b) 加速 ROS 上运行的应用。

本文提出一种能够实现上述目标的架构。该架构由一套 ROS 2 包构成,能够将硬件加速集成到 ROS 工作空间。这种架构适用于各种平台(瞄准支持边缘、工作站、数据中心或云)和各种技术(支持 FPGA 和 GPU),并且能够轻松地移植到其他电路板上。该架构的核心组件已经在 Apache 2.0 许可证下公开,对三种电路板的基本支持也已通过演示。此外,提供的架构还适用于各种应用,将来可以通过包含 catkin 扩展( 非 ament)轻松移植到 ROS。

连载二:工业类比CPU/GPU,ASIC和FPGA,谁更适合机器人计算

CPU 和通用 GPU (GPGPU) 是两种广泛使用的商业计算平台,因为它们可用性高且具有通用性。这些计算技术的通用性,是机器人专家对其特别感兴趣的原因。但是通用性的代价是:

1.通用平台的固定架构难以适应新的机器人场景。追加功能往往需要追加硬件,这也往往意味着要花时间对新的硬件进行新的系统集成度。

2.通用性必然导致其在时效上的缺陷,从而影响确定性形成(难以满足严格的实时性要求)。

3.其功耗通常比专用计算架构(如 FPGA 或 ASIC)高一到两个数量级 (1)。

4.其固定的、不具备灵活应变能力的架构,导致其对网络安全威胁和恶意行为的抵御能力减弱。熔毁 ( Meltdown ) 或者幽灵 ( Spectre ) 等网络攻击示例表明,如果缺乏重新配置数据流流水线的能力,计算平台最终将丧失安全性。

总体而言,CPU、GPU 和 ASIC 等采用固定架构的器件,在其为开发者提供优势的同时,也让其付出了代价。它们所缺乏的灵活应变能力,导致其缺乏时效性,能耗增加。而且由于它们无法通过重新配置架构来提高硬件的抗风险能力,因此在网络威胁面前更加脆弱。

CPU的工业类比

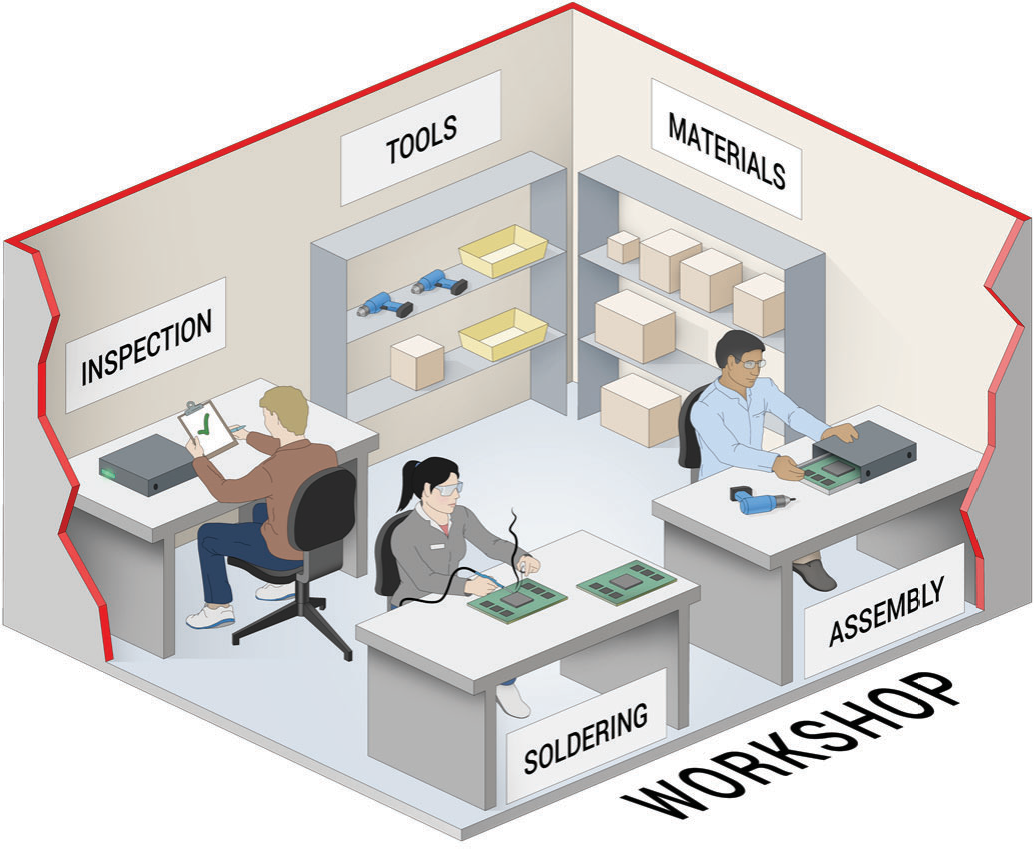

图1是 CPU 的工业类比,它将 CPU 理解成一系列车间,并且每个车间安排一位技能非常娴熟的工人。

图1 CPU 的工业类比

这些工人每人都能使用通用工具生产出几乎任何产品。每位工人按顺序使用不同的工具,将原材料制造为成品,一次生产一件产品。根据任务的性质,这种串行生产流程可能用到大量步骤。这些车间基本(不考虑缓存的情况下)彼此独立,工人能全身心地完成不同任务,不必担心干扰或协调问题。尽管CPU 十分灵活,但它的底层硬件是固定的。CPU 仍然在基本的冯诺依曼架构(或者更确切地说,存储程序计算机)上运行。数据从存储器读取到处理器进行运算,然后写回到存储器。基本上每个 CPU 都以串行方式运行,一次一个指令。同时架构以算术逻辑单元 (ALU) 为中心,每次运算都需要将数据输入到 ALU 并从 ALU 输出数据。

CPU的工业类比

GPU 也可以用车间和工人类比,但它们的数量要大得多,并且工人的专业化程度也要高很多,如图2所示。

图2 GPU 的工业类比

GPU 工人只能使用特定的工具,每人能完成的任务种类要少得多,但他们完成任务的效率非常高。GPU 工人在重复做相同的少量任务时效率最高,尤其是当他们全体同时做同一件事情时。GPU 解决了 CPU 的主要缺陷之一,即并行处理大量数据的能力。

虽然 GPU 比 CPU 拥有非常多的核,但 GPU 采用的依然是固定的硬件架构。GPU 的核仍然包含某种类型的冯诺依曼处理器。一条指令就能处理上千条或者更多数量的数据,尽管通常必须对同时处理的每一条数据进行相同的运算。原子处理元在数据矢量上运算(非 CPU 情况下的数据点),但仍然是每个 ALU 执行一条固定的指令。因此,用户仍然需要通过固定的数据路径,从存储器将数据传递给这些处理单元。与 CPU 相似,GPU 也采用固定硬件构建,对所有的机器人应用而言,其基本架构和数据流都是固定不变的。

FPGA 的工业类比

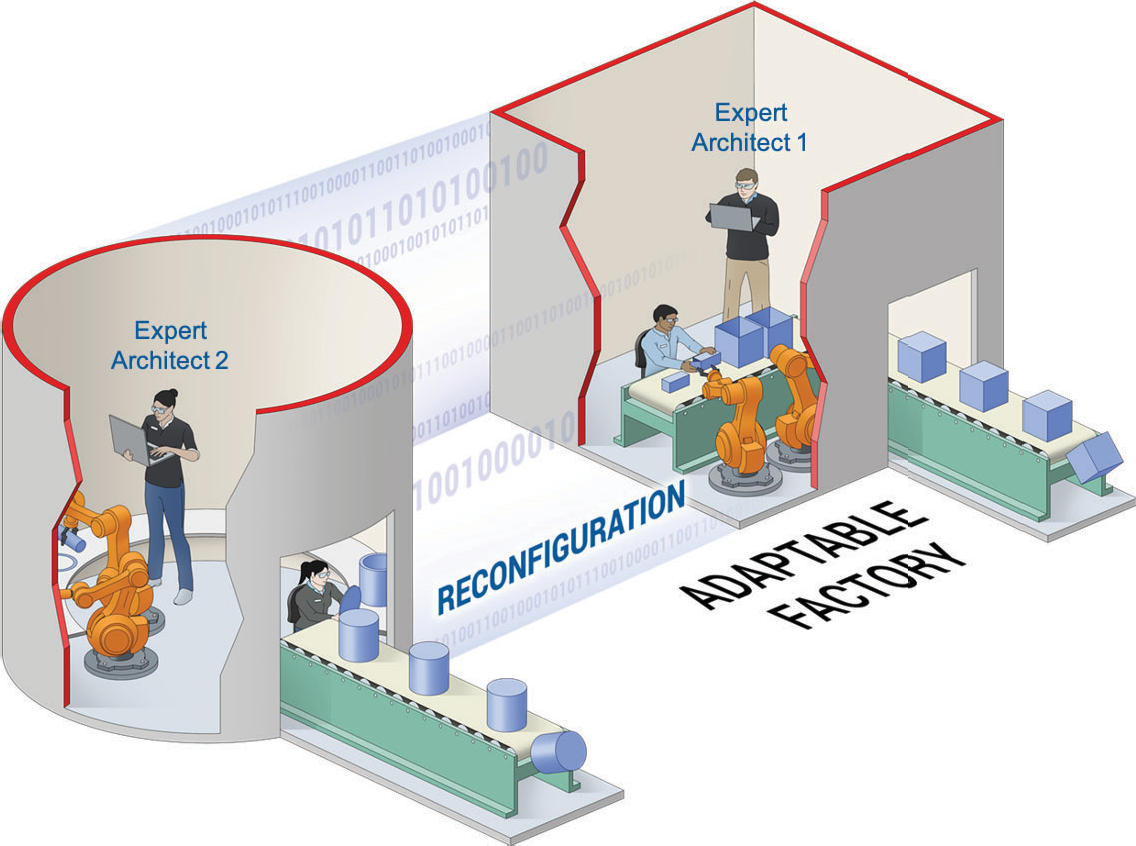

如果说 CPU 和 GPU 是工人按照顺序依次将输入加工成输出的车间,那么 FPGA 就是灵活的自适应工厂,能够针对手中的具体任务定制创设装配线和传送带(参见图 3)。

图3 FPGA 的工业类比

这种灵活应变能力,意味着 FPGA 架构师可以先构建工厂、装配线和工位,然后根据所需完成的任务对它们进行量身定制,而不是使用通用工具。这些工厂中的原材料由分配在装配线上的工人小组逐步加工成成品。每名工人都重复地完成同样的任务,同时半成品通过传送带在工人间进行传递。这样能大幅提升生产力,并保证以最佳方式充分利用资源和电力。在这个类比中,工厂是 OpenCL 加速内核,装配线是数据流流水线,工位是 OpenCL 计算功能。

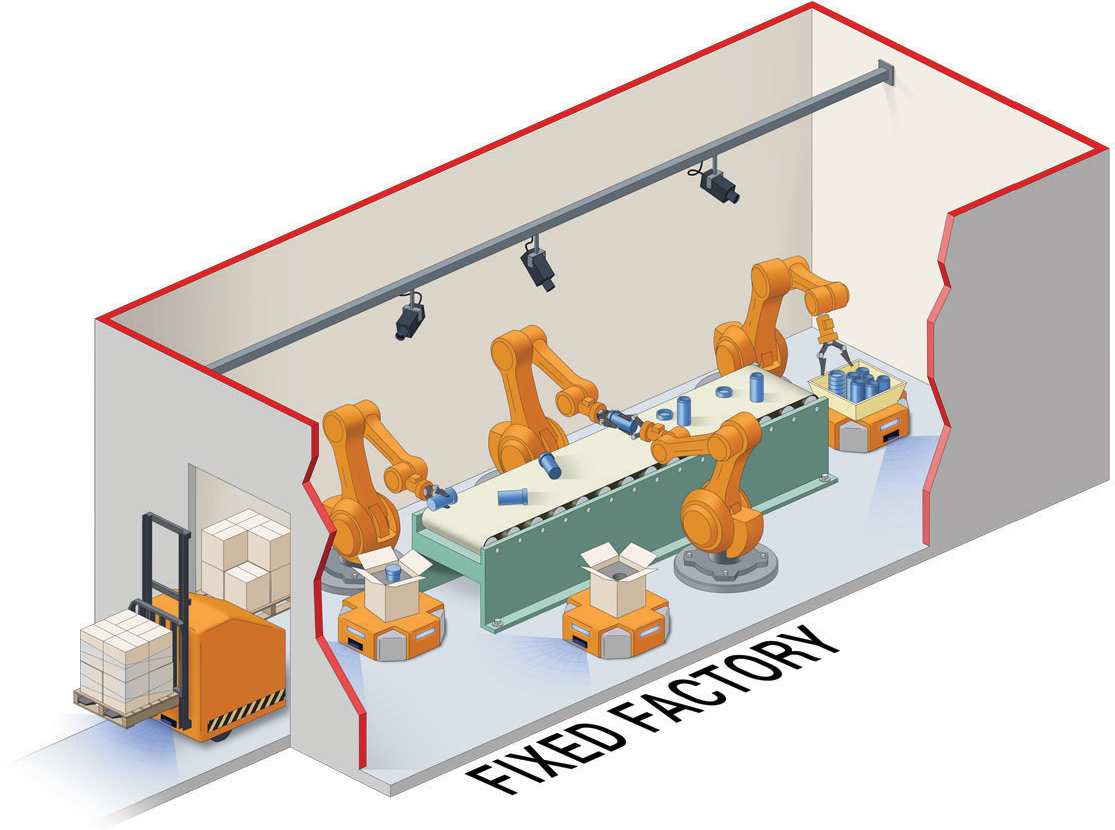

ASIC的工业类比

与 FPGA 类似,ASIC 也建造工厂,但是 ASIC 中的工厂是最终形态,不能改动(参见图 4)。换言之,这些 ASIC 内部只有机器人,工厂内不存在人类认知。这些装配线和传送带是固定的,不允许变更自动化流程。ASIC 的这种专用型固定架构赋予它们极高的能效,以及大批量规模化生产下的最低价格。但遗憾的是,ASIC 的开发通常需要耗时多年,而且不支持进行任何变更,这将会导致前期投入的资产很快跟不上未来生产力提升的变化。

图4 ASIC 的工业类比

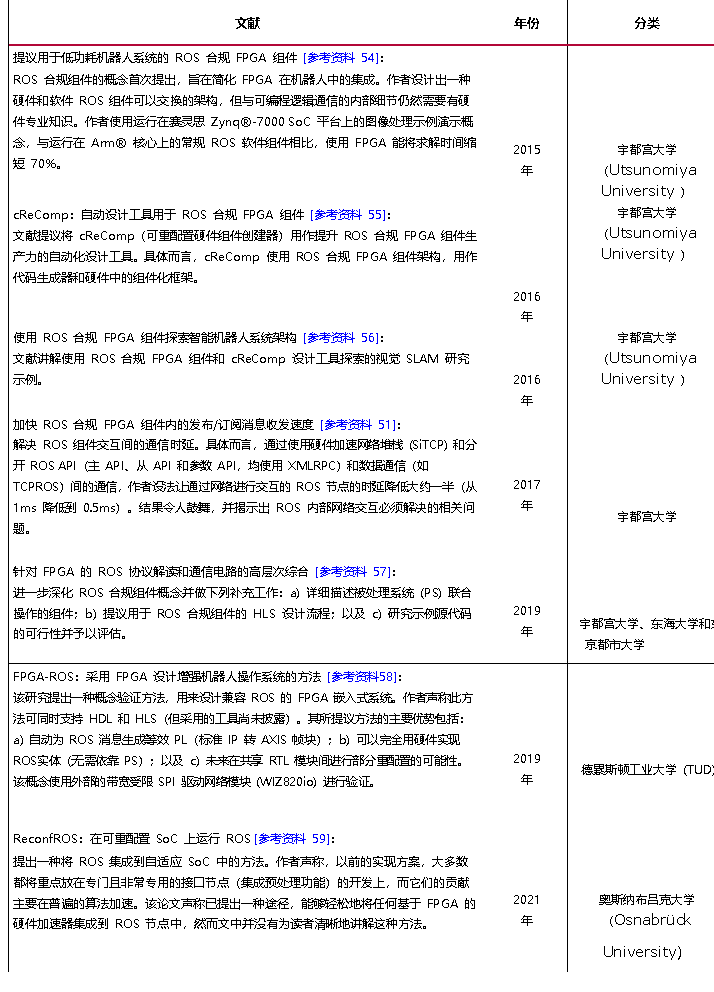

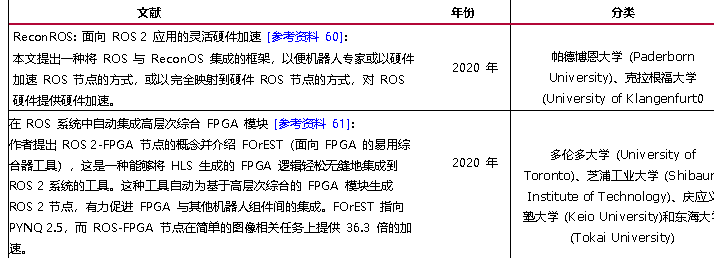

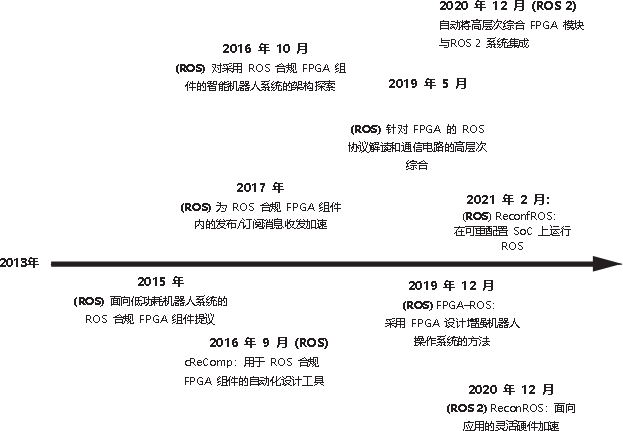

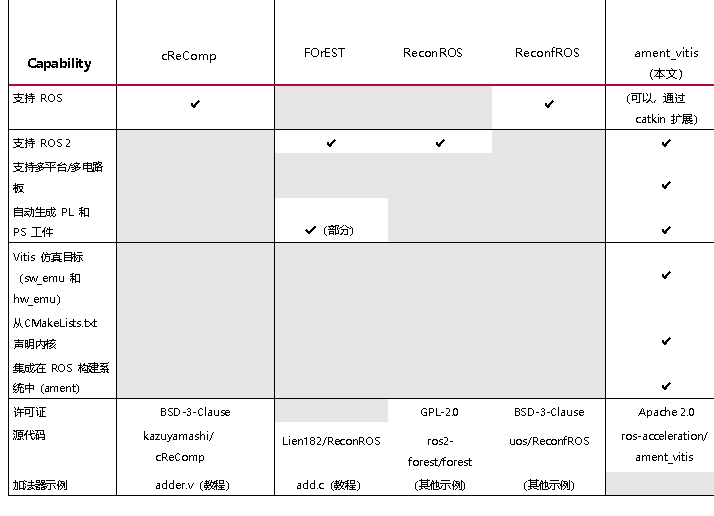

表1和表2总结的是将 ROS 和 ROS 2 分别实现在图 1 所示一些自适应计算平台的既往研究。图 4 所示的是历年来最具相关性的成果。

图 1 赛灵思自适应计算解决方案

表1 在自适应计算平台上实现 ROS 的既往研究

表2 有关在自适应计算平台上运行 ROS 的既往研究

图2 ROS 与 ROS 2 演进变革

图2反映出科研界对促进自适应计算发展的兴趣越来越浓厚。从 ROS 的角度来看,可以将过去的研究分为三类:第一类研究提出帮助机器人专家充分利用硬件加速功能,将 ROS 计算图的一部分卸载到可编程逻辑 (FPGA) 并进行加速的工具和方法。第二类研究提出加速 ROS 底层的概念,特别是用网络堆栈优化节点间的网络内交互。根据"Real-time Linux communications: an evaluation of the linux communication stack for real- time robotic applications"的描述,网络堆栈是 ROS 通信的瓶颈,"Acceleration of publish/subscribe messaging in ROS-compliant FPGA component"等研究对实时分布式系统有参考价值。第三类研究提出用自适应计算优化 ROS 计算图。

除了在用户空间层面加速特定应用和 ROS 库,值得一提的还有在流程间、流程内乃至网络内的层面上加速 ROS 节点间的交互。由于机器人行为建立在 ROS 节点交互的结果之上,因此用于这个用途的加速器通过从总体上减少 ROS 和 ROS 2 计算图数据流,显著影响总时延。也就是说,在考虑 ROS 和 ROS 2 时,必须应用全面的硬件加速视图。这种视图能体现:a) 对流程中、流程内、网络内(含底层) ROS 计算图交互的优化;以及 b) 对 ROS 上运行的应用的加速。

要点总结:在考虑 ROS 和 ROS 2 时,必须应用全面的硬件加速视图。这种视图能体现:a) 对流程中、流程内、网络内(含底层)的 ROS 计算图交互的优化;以及 b) 对 ROS 上运行的应用的加速。

根据图 2 列出的既往研究,还可以得出另一个结论。过去的大多数方法主要都是从硬件工程师的视角解决自适应计算与 ROS 的集成问题,其提出的大多数工具和方法都有一个先决条件,即最终用户必须具备嵌入式流和硬件流的既有经验。这往往意味着需要熟悉 RTL、HDL 和 HLS 等概念,或能熟练使用 Vivado® 设计套件或 Vitis™ 统一软件平台等工具。类似地,部署到嵌入式目标也需要用户在一定程度上熟悉 Yocto,OpenEmbedded 以及相关工具。大多数从事 ROS 研发的机器人专家不具备这样的能力。要集成自适应计算,需要采用一种以 ROS 为中心的方法。硬件和嵌入式流程必须直接集成到 ROS 生态系统中,提供的体验与机器人专家在其桌面工作站上构建 ROS 工作空间时的体验相似。在充分利用所有既往研究结果和经验的基础上,下一章节将提出一种以 ROS 为中心的架构,用于集成自适应计算。

连载七:用ROS 2 在机器人内部集成自适应计算的新架构

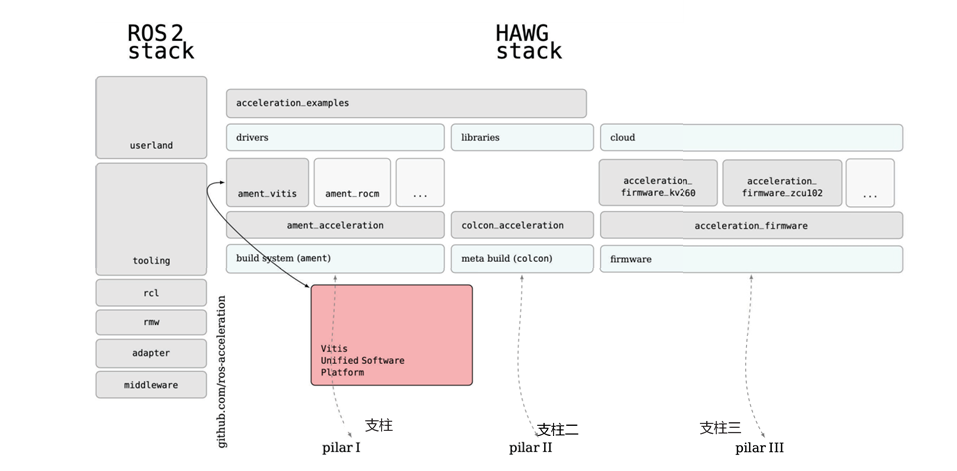

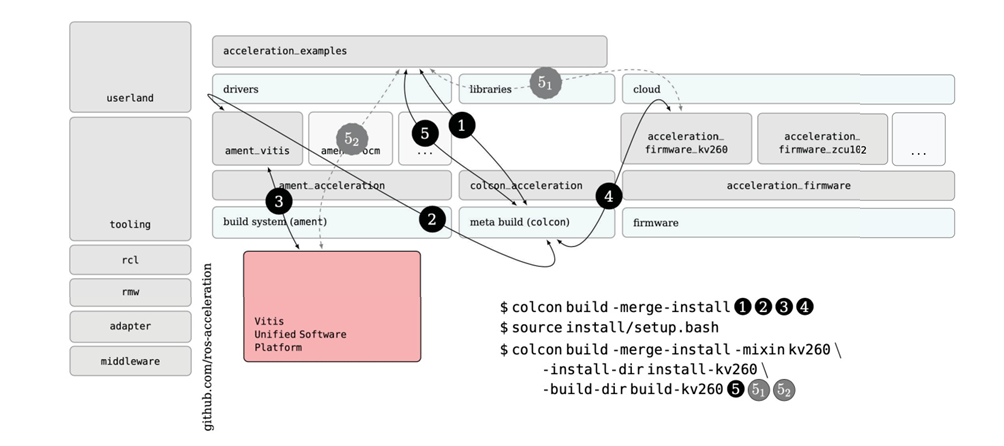

图 1 所示的架构将硬件加速集成到 ROS 2 中,同时坚持以机器人专家为中心的理念。不要求熟悉非 ROS 工具(如 Vivado 或 Vitis 工具),或熟悉 OpenEmbedded 或 Yocto。此外,该架构构建在开放的标准之上,以 C++ 和 OpenCL 作为生成加速内核的目标计算语言。通过这种方法,机器人领域的大多数用户都可以受益于硬件加速的功能。该架构基于三大支柱构建:ROS 构建系统 (ament)、ROS 元构建工具 (colcon) 以及嵌入式固件 (firmware)。

图1 ROS 2 硬件加速工作组 (HAWG) 初始架构

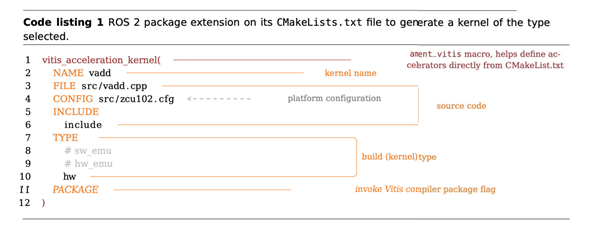

第一个支柱是 ament ROS 2 构建系统的扩展。ament_vitis(1)通过一系列 CMake 宏和实用工具实现这些扩展,将 Vitis 工具包含到 ROS 2 生态系统内。提议的架构是一种适用于几乎任何加速技术的架构,即 ament_acceleration 抽象层从框架和软件平台(如 Vitis 工具)抽象构建系统扩展,为 FPGA 和 GPU 提供支持。作为替代加速技术的例子,图 10 里包含了 ament_rocm,展现未来集成 ROCm5(2)软件开发平台的潜力,以实现 HPC/超大规模级 GPU 计算。在后台,ament_acceleration 的每次专门优化都需要对应的库。例如,ament_vitis 依靠 Vitis 和赛灵思运行时 (XRT) 库(3)。后者是一种开源的标准化软件接口,用于简化应用代码和加速内核之间的通信。Vitis 工具和 XRT 完全对机器人工程师隐藏,不仅简化了加速内核的创建,而且还帮助机器人专家专注于计算图像的改进。通过提供犹如任何其他 ROS 封装的体验,以这种方式实现简化加速内核创建工作的目标。图 2 所示的代码列表 1 展示的是使用 ament_vitis ROS 封装的示例。宏 vitis_acceleration_kernel 提供灵活性,允许用户无缝地扩展CMakeLists.txt 并选择加速 ROS 封装的哪些部分。

图2 代码列表 1

第二个支柱扩展“colcon”ROS 元构建工具,以集成硬件加速专用流。

第三个支柱是嵌入式固件。表达为 acceleration_firmware(1),第三个支柱旨在为硬件加速平台提供固件专用工件,这样就能针对这些工件编译加速内核,从而简化流程并保持ROS 开发流程。提出的架构在构建时特意考虑到各种硬件加速平台,可以支持边缘(嵌入式)器件,以及适用于工作站、数据中心乃至云硬件加速的 PCIe® 加速器。平台选择通过在 ROS 工作空间资源(在 src/ 下)中加入特定的 acceleration_firmware 库(acceleration_firmware_xilinx)来实现。构建过程中的平台选择(本例中为赛灵思 Zynq UltraScale+™ MPSoC ZCU102 平台)通过 colcon mixins 来实现。通过这种方式,colcon build -build- base=build-zcu102 -install-base=install-zcu102 -merge-install -mixin zcu102 将为 ZCU102 硬件平台构建完整的 ROS 2 工作空间,交叉编译 ROS 封装,在运行中视情况为 ZCU102 平台生成内核。所有中间步骤完全实现自动化,而且产生的 install-zcu102 目录能直接在硬件中使用。

为了容纳中间工件并在嵌入式流程中提供灵活性,acceleration_firmware 在 ROS 2 工作空间中引入新的子文件夹结构,即 <ros2-workspace-path>/acceleration/firmware/<platform> 路径。

图 3 是 acceleration_examples ROS 2 封装构建完成后,该架构的工作方式预演。流程从 colcon 构建 ROS 2 工作空间开始(图 3,插图编号 1)。无需使用特殊的旗标,只是对应的封装和硬件加速工作组 (HAWG) 基础设施必须位于工作空间的 src 目录内。colcon 将为开发工作站架构构建每一个封装。这其中包含 ament_vitis Cmake 宏(图 3,插图编号 1),该宏将一系列 CMake 扩展部署到产生的本地 ROS 2 叠加工作空间中。

这些扩展与本地 Vitis 安装(1)(图 3,插图编号 3)相连,对ROS 2 包直接提供其功能。换句话说,ROS 2 包能从它们的 CMakeLists.txt 文件使用这些宏,并且使用赛灵思的硬件加速工具。

固件包(如 acceleration_firmware_kv260)是该架构的重要组件。切换加速器时,只需用适用于新的目标加速器的包替换这个包即可。任意一个有效的固件包都应包含固件工件和 CMake 逻辑,以便在 ROS 叠加工作空间中正确地为实现硬件加速目的而解包、部署和配置固件(图 3,插图编号 4)。此外,有效的固件包应包含根文件系统、根文件系统的 sysroot(用于交叉编译)或在构建时自动生成 ROS 2 mixins(2) 的模板,以简化嵌入式流程和其他方面。如需进一步详细了解,请参阅任何官方固件包的完整工件列表。

总之,首先调用 colcon 构建(图 3,插图编号 3),让 ROS 2 工作空间为硬件加速做好准备并将文件部署在本地叠加内(图 3,插图编号 2、3 和 4)。在此之后,从本地叠加第二次调用带 -mixin<target-board> 旗标的 colcon 构建,将进行交叉编译(图 3,插图编号 51)并根据需要为目标加速器硬件生成加速器(图 3,插图编号 52)。从这一点开始,colcon_acceleration 包有助于其余流程的进一步自动化。这部分已超出本文所要探讨的内容。

下列三种不同的电路开发板已经获得基本支持:赛灵思 Zynq UltraScale+ MPSoC ZCU102,ZCU104 以及 Kria™ KV260 视觉 AI 入门套件。

图3 HAWG 初始架构内 ROS 2 包之间的交互走查

要点总结:在既往研究的启发下,当前研究提出一种以 ROS 2 为中心的架构,让硬件加速在 ROS 生态系统中发挥关键作用。图 12 体现的提议被模块化成不同的 ROS 2 包,它们的构建方式与任何其他 ROS 包一样。这种架构适用于各种平台(瞄准边缘、工作站、数据中心或云提供支持),也适用于各种技术(支持 FPGA 和 GPU ),并且只需提供对应的专业 acceleration_firmware,就能轻松地将其移植到其他电路板。

表 4 总结了这里提出的方法与以前的工作的比较。

表4 ROS 与 ROS 2 各类自适应计算集成方法比较表(含赛灵思 ament_vitis)

资源获取:

1. 如需获取 ament_vitis,请访问链接:https://github.com/ros-acceleration/ament_vitis

2. 如需获取 ROCm,请访问链接:https://github.com/RadeonOpenCompute/ROCm

3. 如需获取 XRT,请访问链接:https://github.com/Xilinx/XRT

4. 如需获取 acceleration_firmware,请访问:https://github.com/ros-acceleration/acceleration_firmware。参见 acceleration_firmware_xilinx,查看专为赛灵思平台优化的具体示例。

评论