宽带数字接收机的研究及实现

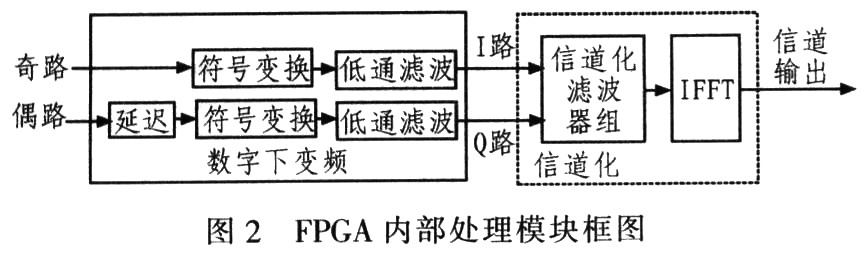

DDC后得到的基带信号进入信道化滤波器组完成信道化处理,可得到32路子带信号,此时每个子带信号的速率降为300~32 MHz,从而大大减轻后续信号处理负担。图2是FPGA内部处理模块框图。本文引用地址:http://www.eepw.com.cn/article/201809/388980.htm

2.3.1 数字下变频DDC

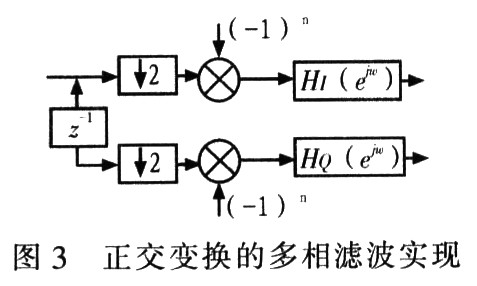

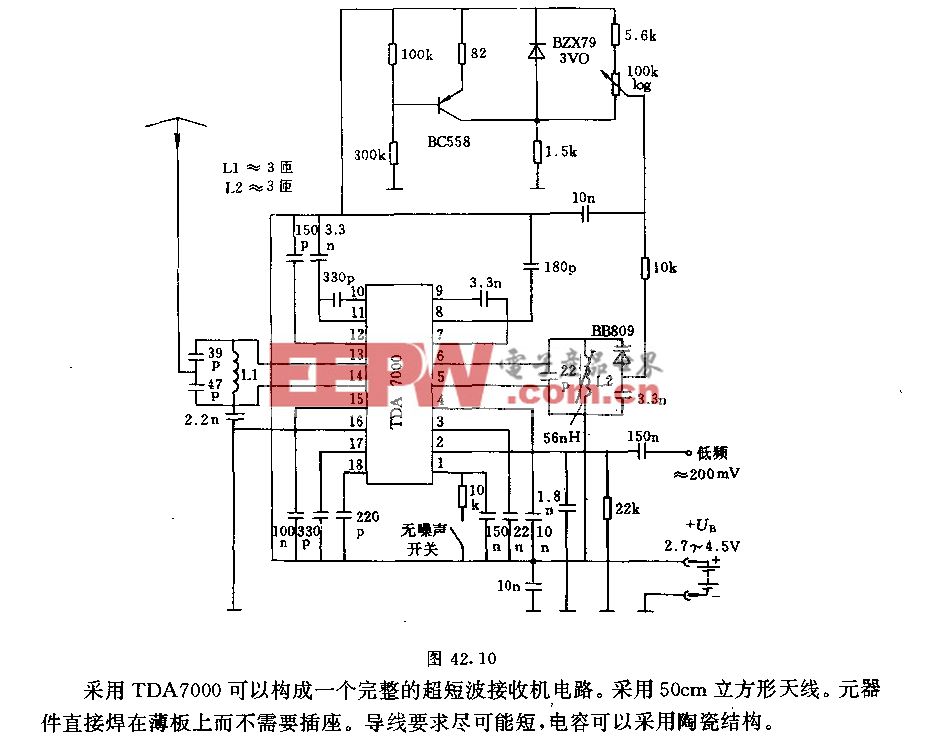

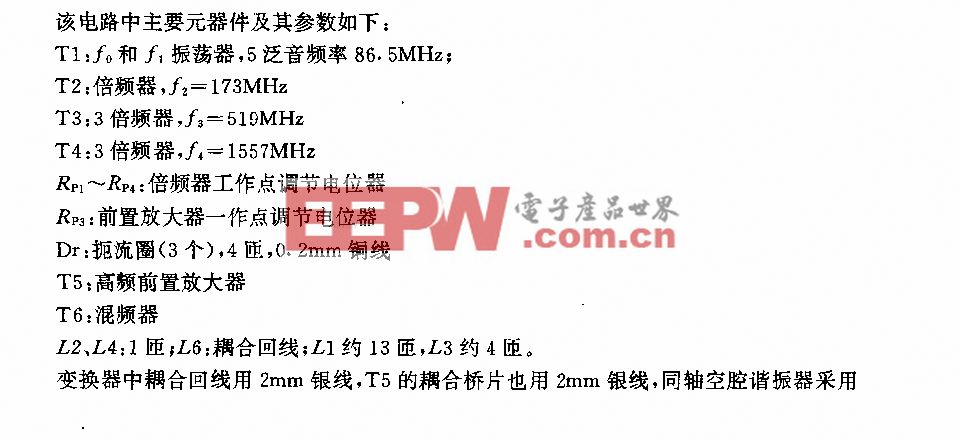

A/D转换器的输出信号为LVDS形式,进入FPGA后需转换为单端信号。采用 Altera公司提供的模块完成信号转换。由于A/D转换器采用偏移二进制,需转换为补码形式。数字下变频是将高速率信号变成低速率基带信号,以便进一步作信号处理。典型的数字下变频采用乘法器和NCO实现,其缺点:A/D转换器需在高频下采样数字化;当采样速率很高时,后续数字低通滤波则成为瓶颈,特别是当滤波器阶数很高时:低通滤波后抽取,这意味着有很多经下变频和低通滤波后的数据都未被利用,浪费大量运算结果,运算效率低。因此,这里提出一种基于多相结构的高效宽带数字下变频结构,如图3正交变换的多相滤波实现图3所示。

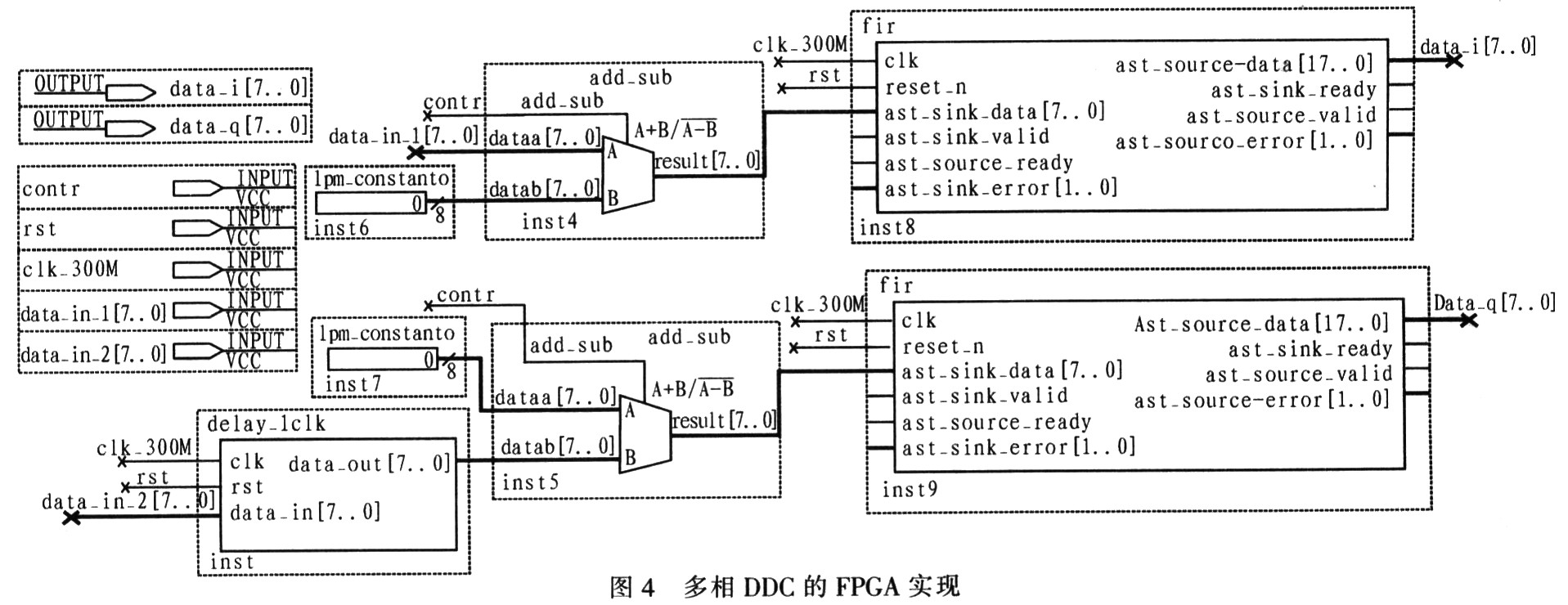

具体实现:2倍抽取在A/D转换器内部通过DMUX完成,然后由符号转换将输人信号正负交替输出,利用加法器实现,加减可控制。

需输出原数据时,加减控制设为加法;需输出反相数据时,则设为减法,输出数据为零减去原数据。FPGA实现如图4所示。

2.3.2 多相信道化滤波器组

经下变频得到I,O两路信号,为得到较高的频率分辨率,采用信道化法。该方法的基本原理是将输入的全带信号进行频带分割,即把接收到的信号频段分解成若干个不同频段(又称子频段或子信道),然后分别处理各子段。为得到更高的频率分辨率,各子频段可分别再进行第2次分割、第3次分割,直到满足频率分辨率的要求。由于该设计的接收机工作在中频,因此只需1次分割即可。

假设侦察系统接收的中频带宽为300 MHz,A/D转换器采样速率为600 MHz,带通采样,无模糊带宽为300 MHz,周期延拓后,中频带宽(300 MHz)落在其中的一个周期内,因此不会产生频率混叠现象。无模糊带宽(300 MHz)分为32个信道,输入分为实部和虚部。各信道带宽是9.375 MHz(300/32)。该系统设计采用基于DFT多相滤波器组的信道化滤波器技术,实现数字信道化滤波器。由于采用预先抽取方式,降低滤波运算的运算量。而IDFT可利用FFT实现。因此系统的数据率降低,实时性能很高。

评论