基于同步降压DC/DC调整器的供电模块设计

随着工艺技术的发展与市场需求,超大规模、高速、低功耗的新型现场可编程逻辑器件(FPGA)不断推出,给电路设计带来极大的方便。在采用大规模FPGA的开发系统中,供电模块的设计将直接影响到系统的稳定性,因此设计出高效、稳定的供电模块显得尤为重要。本文以可扩展网络交换调度系统的FPGA验证平台为例,介绍FPGA供电模块的设计方法。

本文引用地址:https://www.eepw.com.cn/article/201808/387844.htm目前,FPGA、DSP等芯片的电源供电方案主要有三种:低压差线性稳压器(LDO)、电源模块和开关稳压电源。其中采用集成FET的称为DC/DC调整器,采用非集成FET的称为DC/DC控制器。

LDO的基本原理是根据负载电阻的变化情况调节自身的内阻,从而保证稳压器输出端的电压不变,因此LDO只适用于降压变换。其具体效果与输入/输出电压比有关,变换效率可以简单地看作输出与输入电压之比。由于采用线性调节原理,瞬态特性好。LDO本质上没有输出纹波,但随着LDO的输入/输出电压差别增大或者输出电流增加,LDO的发热比会成比例增大,所以在散热控制方面要求很高。LDO稳压器为电流输出要求较低的应用提供了体积小且廉价的解决方案。

DC/DC调整器利用了磁场储能,无论升压、降压或是两者同时进行,都可以实现相当高的变换效率。由于变换效率高,因此发热很小,散热处理得以简化,所以DC/DC调整器一般不再需要附加一个成本较高、面积较大的散热器。考虑到DC/DC调整器集成有FET,使用时只需外接一个电感和必不可少的输入电容和输出电容,故可以使整个解决方案的空间利用率大大提高,尤其对于需要大电流的FPGA来说十分理想。由于是开关稳压器电源,与LDO相比,DC/DC 调整器输出纹波电压较大、瞬时恢复时间较慢、容易产生电磁干扰(EMI)。要取得低纹波、低EMI、低噪声的电源,关键在于电路设计,尤其是输入/输出电容、输出电感的选择和布局。DC/DC调整器占用面积较大。

DC/DC控制器和DC/DC调整器的差别主要是没有内置的FET。因此,设计者可以选用有特定导通电阻的外接FET晶体管,并根据应用的需要调整电流,使设计具有很大的灵活性,这在需要十几甚至几十安培电流的特大规模FPGA开发系统中非常有用。与DC/DC调整器相比,采用这种方案设计,既要选择适当的输入电容/输出电容、输出电感,又要选择符合要求的FET,增加了设计难度和总成本。此外,由于FET外置,占用空间也相对较大。

电源模块从原理上来说是个开关稳压器,所以它的效率非常高。相对于普通开关稳压器,它的集成度更高,因此外围只需要一个输入电容和一个输出电容即可工作,设计简便,适合要求开发周期非常短的应用。它一般以可插拔的形式给出。由于电源模块上集成了几乎所有可以集成的东西,灵活性相对较差,价格也相对较高。

器件选型与功能介绍

本文中的交换调度系统的FPGA验证平台采用4片Xilinx VirtexII FPGA作为网络包调度器实现可扩展的交换调度功能,其中VirtexII的核心电压VCCINT为1.5V,辅助电压VCCAUX和输出驱动电压 VCCO均为3.3V。由于需要对4片FPGA供电,电源板面积较大。为了调试方便,对整个供电电路采用单独设计制板,根据器件和系统的要求,本设计采用 DC/DC调整器方案。

采用DC/DC调整器的供电方案虽然有多种,但考虑到每个供电模块需要对两片FPGA供电,而且通过仿真估算出的每片FPGA的最大电流为2A左右,加上一定的裕量,因此需要单个供电模块最大能够提供6A左右的电流。

TPS54610是TI公司专门为DSP、ASIC和FPGA等多芯片系统供电而设计的一款低电压输入、大电流输出的同步降压DC/DC调整器,内含 30MΩ、12A峰值电流的MOSFET开关管,最大可输出6A电流。输出电压从0.9V到3.3V可调,误差率为1%。开关频率可固定在350kHz或 550kHz,也可以在280kHz到700kHz之间调整。另外,它还具有限流电路、低压闭锁电路和过热关断电路。而且TPS54610的集成化设计又减少了元件数量和体积,因此,可广泛用于低电压输入、大电流输出的分散电源系统中。经过分析,采用两片TPS54610为两片FPGA供电的方案。

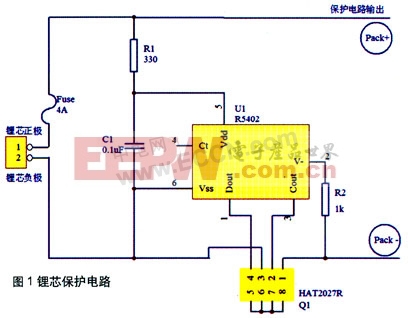

TPS54610采用28脚TSSOP封装,其引脚排列如图1所示。各引脚功能如下:

·AGND(1脚):模拟地。

·VSENSE(2脚):误差放大反馈输入,通过补偿网络/输出分压器连接输出电压。

·COMP(3脚):误差放大器输出,COMP脚与VSENSE脚间应接频率补偿电路。

·PWRGD(4脚):当VSENSE端的电压高于Vref的90%时,输出为高,否则为低。

·BOOT(5脚):自举电路输出,在BOOT脚和PH脚之间应连接0.022μF~0.1μF的电容。

·PH(6~14脚):相输出,功率MOSFET高低端与输出电感的连接点。

·PGND(15~19脚):电源地,使用时应与AGND单点连接。

·VIN(20~24脚):电源输入,与PGND间应连接10μF的电容。

·VBIAS(25脚):内部偏压调节,与AGND引脚间应接一个0.1μF~1μF的陶瓷电容。

·SS/ENA(26脚):软启动/输入输出使能端,可提供控制器允许工作逻辑信号。 该脚的另一个功能是通过外接电容设置软启动时间。

评论