基于IBIS模型的信号完整性分析

在您努力想要稳定板上的各种信号时,信号完整性问题会带来一些麻烦。IBIS 模型是解决这些问题的一种简单方法。您可以利用 IBIS 模型提取出一些重要的变量,用于进行信号完整性计算和寻找 PCB 设计的解决方案。您从 IBIS 模型提取的各种值是信号完整性设计计算不可或缺的组成部分。

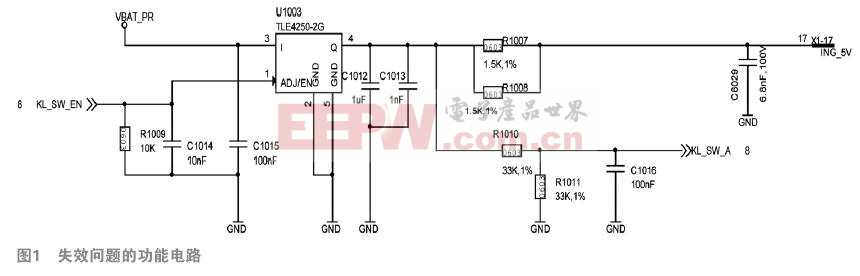

本文引用地址:https://www.eepw.com.cn/article/201706/348350.htm当您在您的系统中处理传输线路匹配问题时,您需要了解集成电路和PCB线路的电阻抗和特性。图 1 显示了一条单端传输线路的结构图。

图 1 连接发射器、传输线路和接收器组件的单端传输线路

就传输线路而言,我们可以从 IC IBIS 模型提取IC的发射器输出阻抗 (ZT, Ω)和接收器输入阻抗(ZR, Ω)。许多时候,IC 厂商产品说明书中并没有说明这些集成电路 (IC) 规范,但是您可以通过IBIS模型获得所有这些值。

您可以用下面四个参数定义传输线路:特性阻抗(Z0, Ω)、板传播延迟(D, ps/in)、线路传播延迟(tD,秒)和线迹长度(LENGTH,英寸)。一般而言,FR-4 电路板的 Z0 范围为 50Ω到75Ω,而 D 的范围为 140 ps/in 到 180 ps/in。Z0 和D 的实际值取决于实际传输线路的材料和物理尺寸(《参考文献 1》)。特定电路板上的线路延迟(tD)等于传播延迟(D)乘以您所使用线迹的长度(LENGTH)。所有板的计算方法均为:

D = 1012 (CTR * LTR) or

D = 85 ps/in * (er)

Z0 = (LTR/CTR)

tD = D * LENGTH

使用 FR-4 板时,合理的带状线传播延迟为 178 ps/ 英寸,特性阻抗为 50Ω。

用于信号完整性评估的发射器规格为输出阻抗 (ZT)。确定输出阻抗时,IBIS 模型中的 [Pin] 区提供每个引脚的电阻、电感和电容寄生值。之后,您可以将封装电容与各个缓冲器的电容值(C_comp)放在一起,以便于更清楚地了解。

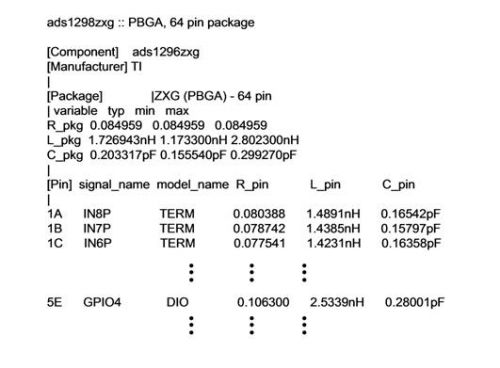

正如 [Pin] 关键字上面的 [Component]、[Manufacturer] 和 [Package] 描述的那样,[Pin] 关键字与具体的封装有关。您会在[Pin]关键字表中找到封装电容和电感,因为它与引脚有关。例如,在ads129x.ibs模型中(《参考文献 2》),图 2 表明了在哪里可以找到引脚 5E(PBGA,64 引脚封装)信号 GPIO4 的 L_pin 值和 C_pin 值。

图 2 包括 C_pin 值在内的 ads1296zxg 封装的封装列表

该信号和封装的 L_pin(引脚电感)和 C_pin(引脚电容)分别为 1.489 Nh 和 0.28001 pF。

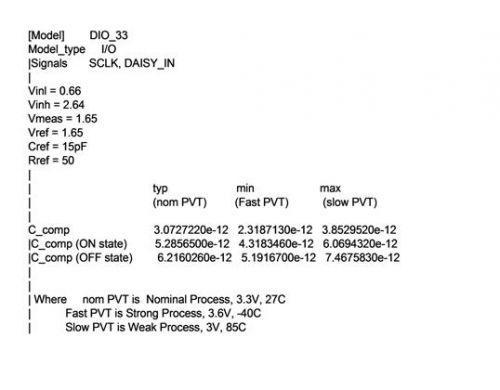

第二个重要的电容值是 [Model] 关键字下面的 C_comp 值。正如您在 IBIS 模型中找到正确的模型一样,您也会找到一份 C_comp 值的列表。图 3 显示了 DIO_33模型中 C_comp 的一个例子(《参考文献 2》)。

图 3 ads129x.ibs 中,其为 Model DIO_33 及其相关 C_comp 值的列表。

在图 3 的声明中,“|”符号表示一段注释。该声明中的有效 C_comp(《参考文献 3》)列表为:

| typ min max

| (nom PVT) (Fast PVT) (slow PVT)

C_comp 3.0727220e-12 2.3187130e-12 3.8529520e-12

通过该列表,PCB 设计人员可以在三个值之中做出选择。在 PCB 传输线路设计阶段,3.072722 Pf 的典型值是正确的选择。

IBIS 模型为 PCB 设计人员提供了一些线索,让他们可以在转到样机设计以前进行板模拟。如果您知道了查找的方法,IBIS 模型就可以为您提供所有引脚的特性阻抗和电容。评估工作的下一步是确定每个缓冲器的输入/输出电阻,我们将在下次为您介绍。

评论