星载计算机双冗余CAN总线模块设计与实现

摘要:随着新型SoC(System On a Chip)集成技术在航天技术中的应用越来越广泛,传统的星载板级设计转为SoC芯片级设计逐渐成为趋势。基于IP—cores(the integration of complex building blocks)复用的SoC技术,是卫星研制中降低设计时间和成本行之有效的方法。本文以商用器件SmartFusion2为平台,以CAN总线数据采集系统为例,阐述了CAN总线模块的冗余架构设计和IP核复用技术,此方案不仅满足了星载计算机平台高集成度、低功耗、也提高了星载通讯网络的稳定性和可靠性。

本文引用地址:http://www.eepw.com.cn/article/201610/306099.htm随着电子技术的进步和芯片集成化技术的发展,卫星平台电子设备呈现小型化、集约化、智能化的发展趋势。SoC(System On a Chip)作为一种新的系统集成技术,可以将一个单板系统甚至整个控制系统的功能集成在一块芯片中实现,不仅可以提高星载电子设备集成度,减小体积重量,提高功能密度,而且可以提高性能和系统的总体可靠。

本文采用基于Flash为基础的SmartFusion2系列FPGA芯片作为星载计算机平台,该芯片将可配置模拟部件、大容量Flash内存构件、全面的时钟生成和管理电路,以及基于Flash的高性能可编程逻辑模块集成在单片器件中。与此同时,FPGA内部集成了高效的ARM内核——Cortex— M3,可以直接替换传统的MCU+FPGA组合。

1 系统综述

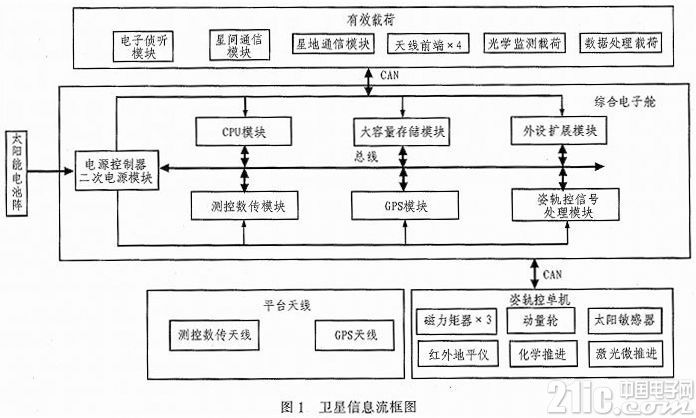

星载计算机作为卫星平台的核心部件,采用总线网络与星载其他电子设备进行互连通信,实现对卫星的多模块控制、星上资源的优化与重组、整星综合信息处理等工作。本系统采用CAN总线将各个单机模块连接在一起,构建一个可以有效的支持分布式控制的串行通信网络。

综合电子舱内部集成了多个模块,以Cortex—m3微控制器作为主控制单元,各单机模块传送的数据通过特定的通信接口将控制信号送给星载计算机微控制器模块,并进行统一的数据处理与任务调度。系统平台包含大容量存储管理单元模块,大容量存储管理单元由独立的处理器接受载荷的数据并存储到4G bits的flash,根据中央处理单元的要求对大容量存储单元进行操作,为存储载荷的有效数据提供了保障。

卫星系统功能与信息流如图1所示。

2 硬件设计

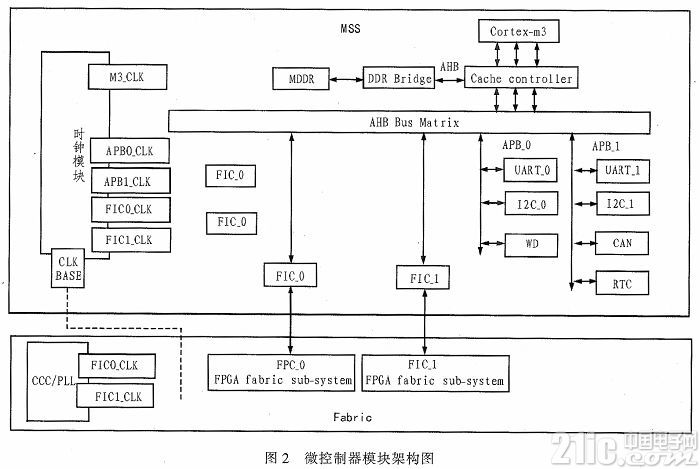

2.1 微控制器模块设计

微控制器模块是综合电子舱的核心模块,主要负责集中完成星上的数据处理、卫星飞行控制任务和姿态轨道数据处理等。基于商用器件SmartFusion2为平台的星载计算机,集成FPGA、ARM Cortex—M3处理器硬核,以及可编程模拟资源于一体的器件,能够实现完全可定制系统设计和IP保护能力,而且便于实现软硬件协同设计。FPGA模块提供的资源如图2所示,主要包括:500000逻辑门单元,大于1 Mbit的RAM模块,可用I/O引脚数大于300个。FPGA内嵌的处理器内核是Cortex-M3,主频为166 MHZ,支持的外设有10/100/Mbps的网络,USB2.0接口、CAN2.0控制器接口、UART串行调试接口等。存储单元主要存储系统的应用程序代码及记录数据,由NOR FLASH存储器和DDRSDRAM组成。主内存是系统运行时代码执行的区域,也是应用程序临时变量和中间数据的存放空间,它的读写速度直接影响到了系统的计算效率,因此需要尽量提高主内存的访问速度和空间大小。本系统中使用DDR SDRAM作为系统的主内存,保证内存访问时间和内存容量不会成为影响系统性能的瓶颈。

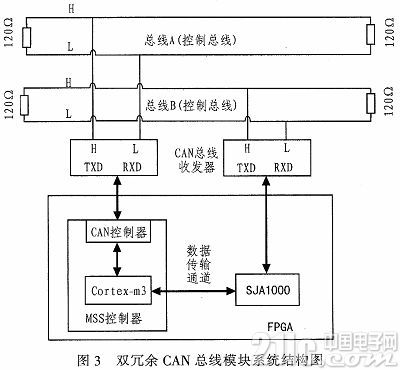

2.2 CAN模块设计

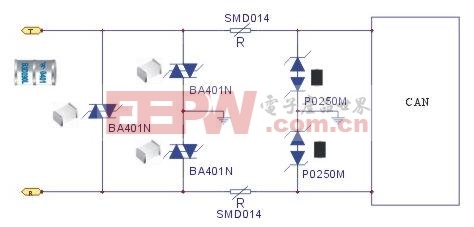

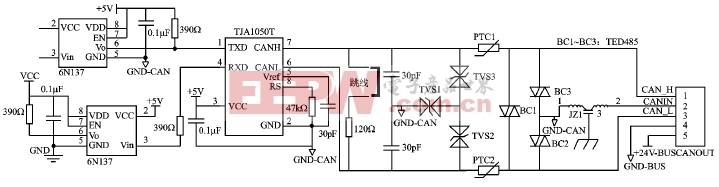

由于星载计算机本身处在恶劣的工作环境,在系统设计开发时必须首要考虑其本身的可靠性及容错能力,所以为保证通信接口的可靠性,本系统采用冗余备份模式设计CAN接口模块。硬件逻辑结构如图3所示,CAN总线冗余设计采用控制器冗余模式,由两个CAN收发器、两个CAN控制器和单CPU组成。两条数据通道完全独立、互不影响。与此同时,双CAN模块采用热备份工作模式,主用设备和备用设备同时处于上电运行状态,且同步进行数据采集、数据处理和计算。但是备份设备的数据处理不起作用,仅当主用设备失效时,CPU才会选择快速响应备用设备的中断,并接收备用设备的数据。

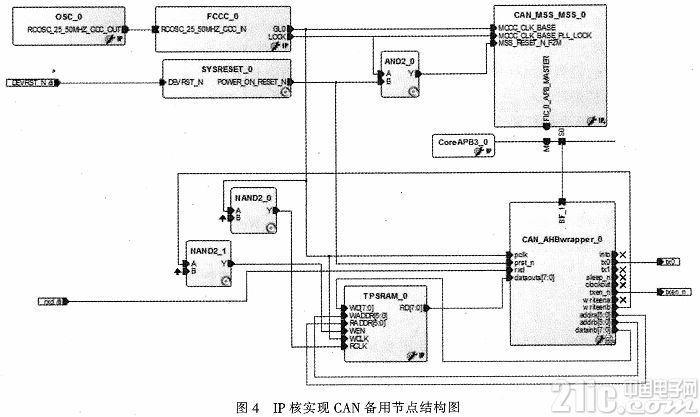

2.3 CAN总线冗余模块设计

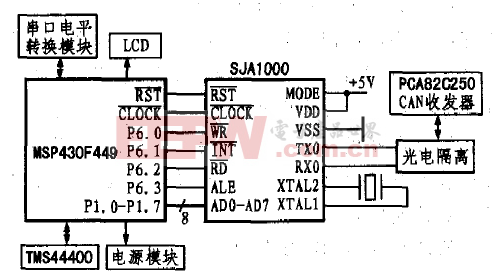

基于SmartFusion2的SoC设计平台仅在APB_1总线上挂载了单一CAN2.0控制接口,为实现硬件冗余设计,利用了SoC提供的FPGA可编程逻辑资源实现了独立的SJA1000CAN控制器。

如图4所示,由VHDL语言设计实现SJA1000 CAN IP软核的设计并生成系统可配置的动态模块,主控单元Cortex—M3通过高级外设总线(APB3)总线接口将数据输出,CAN总线控制器经过一个SRAM(报文缓冲器)与从设备实现通信并对数据报文进行预处理。

HDL程序在Libero IDE集成环境中完成,使用VHDL硬件描述语言编写代码,并编写相关的测试代码进行功能验证。

3 软件设计

CAN总线控制器的功能配置和行为由主控制器Cortex—M3设置的C程序完成,在SoftConsole集成开发环境中完成。

根据SJA1000设计的CAN控制器和微控制器自带的CAN控制器构成了CAN总线上的双冗余备份模式。两者在内存中的映射起始地址分别为:0x40015000u和0x70000000u。由于两种CAN控制器的IP核不同,需要根据每个控制器采用的协议设计CAN设备的驱动程序。

1)单节点驱动设计

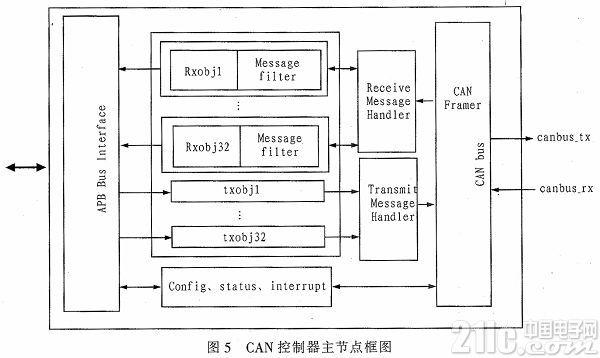

Cortex—M3内部集成的CAN控制器对如图5所示,控制器从CAN总线上接收和发送串行数据,并将数据传递给报文处理器。报文处理器基于当前的过滤设置以及报文对象存储器中的标识符,将合适的报文内容载入与之对应的报文对象。报文处理器还负责根据CAN总线的事件产生中断;报文对象存储器是一组32 个完全相同的存储模块,可为每个报文对象保存其当前的配置、状态以及实际数据。用户可直接配置报文对象存储器完成数据的发送和接收配置。

CAN总线节点的软件设计主要包括CAN节点初始化、报文发送和报文接收。使用控制器之前,需设置CAN的工作时钟(40 MHz)并配置用于传输CAN信息的GPIO管脚。

2)冗余程序设计

系统使用了两条完全独立的CAN总线数据通道,实现了物理层、数据链路层的全面冗余。独立的控制器能够检测到自己通道的故障,但CAN协议规范定义的数据链路层和部分物理层并不完整,需要通过软件冗余模块来实现总线状态的监控、网络故障的诊断和标识处理。

在热冗余的情况下,本地节点主控制器同时打开两个总线控制器的中断。当网络其他节点发送数据帧/请求帧时,如集一个CAN控制器到它相对应的总线上的任一环节发生故

障,则相应的总线控制器不会产生中断,控制器收到的数据则是另一个没有产生故障的总线上的数据。如果本地两个总线控制器同时接收到同一个报文,并分别向主控制器Cort ex—M3申请中断。当有一个总线控制器申请成功时,则在中断服务程序中关闭中断,进行数据处理。如果接收到的报文有效,主控制器则对数据进行处理,处理完毕后,加入低延时、清除所有的中断并在退出前打开所有的中断。另一个CAN总线控制器的中断,如果是同时到达的则被清除,如果是稍后到达的,则会因为中断处理程序的延时也同样会被清除。如果接收到的报文无效,主控制器将清除本次控制器申请的中断,退出中断处理函数。此时,另一个CAN总线控制器的中断会被响应,主控制器会判断接收到的报文是否有

效,并采取相应措施。

4 结束语

本文的设计创新点在于提出了基于SoC技术与IP核复用技术的星载计算机CAN网络模块冗余设计,与传统的星载计算机外扩两片CAN控制器的冗余设计方案相比,本设计充分利用SoC技术实现内置两路CAN控制器,简化电路设计、节省了星载计算机单板体积且采用公开开放免费的软IP以及自行开发的软IP核达到降低成本的目的降低了成本。

评论