基于Microblaze软核FSL总线的门光子计数器设计与实

3.2 通讯协议

Microblaze到计数IP核之间的通讯数据定义如下:本文引用地址:http://www.eepw.com.cn/article/194785.htm

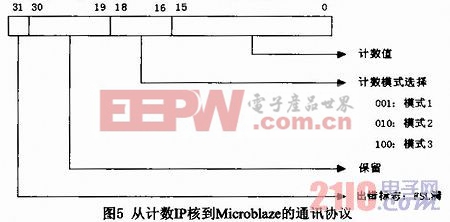

计数IP核到Microblaze之间的通讯数据定义如下:

3.3 计数IP核的设计实现

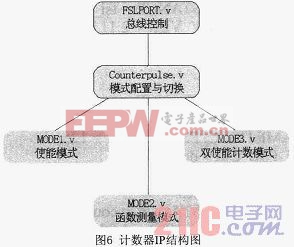

3.3.1 计数IP核的结构

计数IP核采用verilog硬件语言编写,其结构如图6所示,顶层文件counterpulse3对接口进行配置,并根据FSL总线上的命令参数选择工作模式,pulsecount1、pulsecount2和pulsecount3分别是3种工作模式的代码实现,fsloprt是与FSL进行接口的代码。

3.3.2 与FSL总线接口

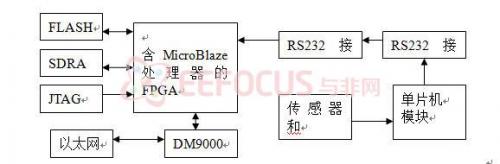

fslopn.v的代码完成与FSL总线接口功能。FSL总线是单向点对点的通道,它用于完成任意FPGA中两个模块的快速通讯。FSL总线是基于FIFO的,基于非共享的无仲裁通信机制,它的深度是可以设置的,最大可以到8k,具备高速的通信性能,其结构如图7所示。

评论