基于Microblaze软核FSL总线的门光子计数器设计与实

2 系统设计实现

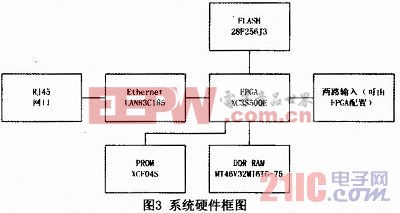

2.1 系统硬件框图

计数系统硬件结构如图3所示,由FPGA、64MB的DDR存储器、16MB的FLASH存储器和10M/100M以太物理层(PHY)等组成。系统工作时,由PC机通过网口发送命令到FPGA,FPGA内部的Microblaze软核配置计数IP核的工作模式,由FPGA通过两路BNC接口对外部计数源进行计数,并将数据在DDRRAM内进行缓冲,最终将这些数据通过网口发送到PC机。本文引用地址:http://www.eepw.com.cn/article/194785.htm

2.2 主要元器件介绍

2.2.1 FPGA芯片及其配置芯片选用

FPGA选用Xilinx公司的Spartan-3E系列XC3S500E,采用先进的90nm制造工艺生产,其器件密度为50万门。Spartan3系列的FPGA是Xilinx公司专门针对大容量、低成本需求的电子设计而开发的,可支持多种电平的I/O标准;含有丰富的逻辑资源。XC3S500E具有360kbits的块RAM、73kbits的分布式RAM、10476个逻辑单元、20个18×18的乘法器和4个DCM时钟管理模块。

FPGA的配置芯片选用的是Xilinx公司的在系统可编程配置芯片XCF04S,该芯片可为XC3S500E提供易于使用、成本低且可重复编程的配置数据存贮方法,该芯片支持IEEE1149.1标准的JTAG边界扫描测试和编程。在本系统设计中,XCF04S主要存放用于引导Microblaze软核及应用程序的引导代码。

2.2.2 存储芯片

系统使用的RAM是Micron Technology公司的DDRSDRAM(MT46V32M16),是一片容量为512Mbit(32Mx16)的16位总线宽度存储芯片,用于上电后加载Microblaze软核代码和应用程序代码,以及对计数数据进行缓冲。FLASH芯片是Intel StrataFlash parallel NORFlash,型号为28F256J3,存储密度为256Mbit,在本系统中用于保存Microblaze软核代码和应用程序代码。

3 功能设计实现

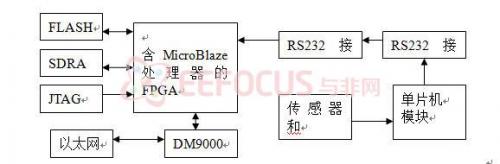

3.1 基于EDK的FPGA软核Microblaze的应用设计实现

系统设计工具主要采用Xilinx公司的嵌入式开发套件EDK,它是用于设计嵌入式处理系统的集成解决方案。它包括搭建硬件平台的XPS和进行软件配置的SDK。

Microblaze是Xilinx公司推出的32位软处理器核,支持CoreConnect总线的标准外设集合。MicroBlaze处理器运行在150MHz时钟下,可提供125 D-MIPS的性能,这种高效的软核在本系统中可用于实现处理器功能,实现对计数IP核的配置,以及支撑Xilinx的clockgenerator、Et-hernet等IP核。系统对计数器的实现采用Verilog语言将计数功能编写为IP核,将其通过FSL总线挂在Microblaze软核上,以实现计数功能。

评论