数字直放站中CPRI协议的FPGA实现

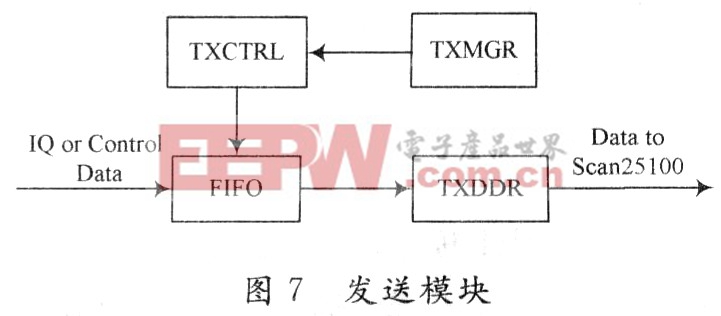

3.2.1 发送模块

按照CPRI基本帧和超帧结构,把DDC(数字下变频)的IQ数据信号与相应的控制信号成帧后发送给SCAN25100,SCAN25100再进行8 B/10 B编码,从光模块发送出去。如图7所示,TXMGR模块产生IQ数据和控制数据的使能信号;TXCTRL模块则对CPRI超帧的控制时隙进行状态转换,产生不同的控制信号,从而从FIFO中选择读出不同的控制信号;TXDDR模块则是把数据通过时钟双边沿进行发送。

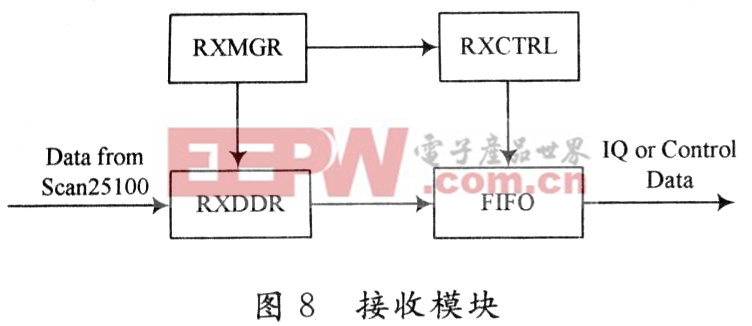

3.2.2 接收模块

将从SCAN25100接收到的数据进行同步头(K28.5)检测,进行CPRI解帧工作,把控制信号和IQ数据信号分解出来,IQ数据信号送到DUC(数字上变频)。如图8所示,RXDDR模块则是通过时钟双边沿接收数据;RxMGR模块通过检测帧头产生IQ数据和控制数据的使能信号;RXCTRL模块则对CPRI超帧的控制时隙进行状态转换,产生不同的控制信号,从而把接收到不同的控制信号写入FIFO,提供给其他模块。

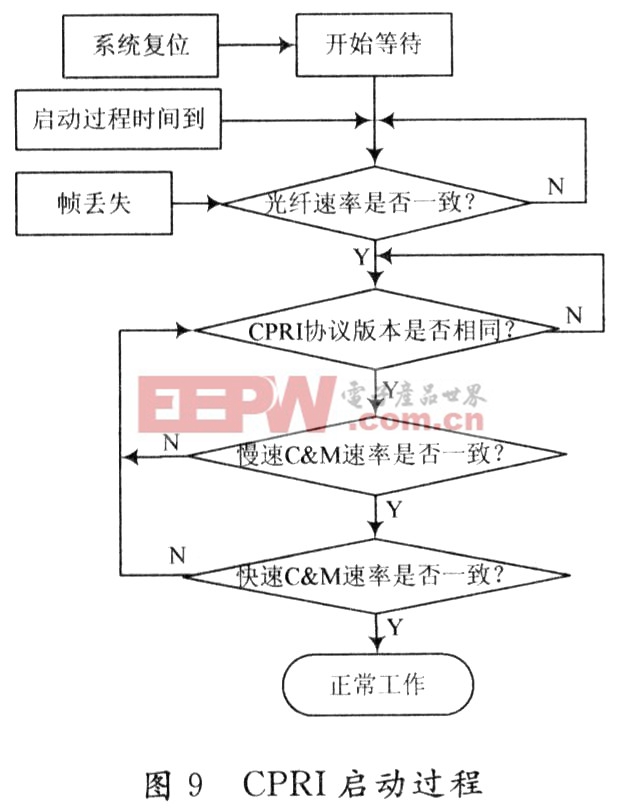

3.2.3 CPRI启动过程模块

CPRI规范中的启动过程,此过程是相当重要的,需要软件和硬件共同完成。协商确定物理层的协议、慢速通道(HDLC)和快速通道(以太网)的传输速率,完成REC和RE之间的链路建立,从而进行正常的通信过程。在设计过程中,理清各个状态的作用,利用状态机实现启动过程,整个流程如图9所示。

4 实际测试结果

4.1 自环测试

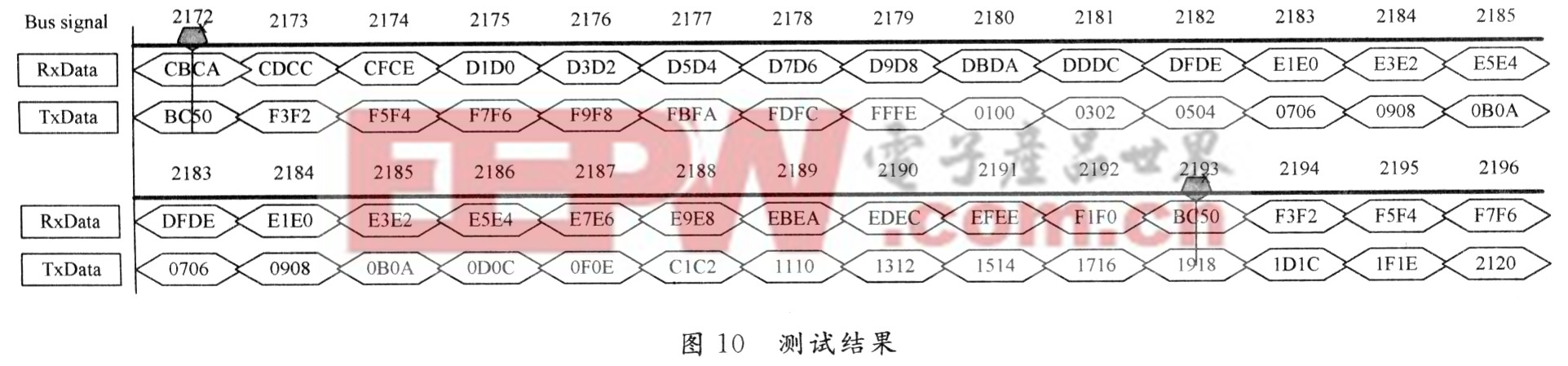

在实验室常温环境下进行实际测试,采用Chips-cope抓取发送和接收的数据进行比较的方法。也就是说,产生一段测试数据,按CPRI帧格式发送给sCAN25100,通过光模块自环回来,如图3所示,然后用Chipscope抓取接收回来的数据,与发送的数据进行对比,确认链路是正常通信。

经过反复测试,该系统已经能正常稳定通信,如图10所示。发送数据(Txdata)帧头为OxBC50,发送时刻为2172,随后的发送数据的高8位和低8位分别以2累加。接收数据(RxData)在2193时刻接收到帧头OXBC50,随后接收到的数据也是高8位和低8位分别以2累加,而且跟发送的数据是一样的。

4.2 联合测试

CPRI模块的成解帧都是在FPGA内部完成的,而数字中频模块(DDC,DUC)也全部在FPGA里面完成设计,如图6所示。两部分的接口显得非常简单,只需要把两部分代码整合成一个工程就行。同样,在实验室常温环境下进行测试,整个系统能正常稳定的工作。

5 结 语

CPRI是规范基站内部REC和RE之间的接口标准协议。该设计把CPRI的两层协议分开设计实现,FPGA实现CPRI链路层,设计灵活。芯片SCAN25100实现物理层,由于芯片具备自动同步及准确校准时延等功能,方便后续设计分布式远程射频基站系统。通过对电路板的实际测试,调整电路设计及PCB部分布线设计,不断地调整优化设计,CPRI模块正常稳定工作,该模块已经和其他模块(DDC,DUC等)通过了联合测试。

评论