基于C P LD的 OMA-L137与ADS1178数据通信设计

1.2 硬件原理

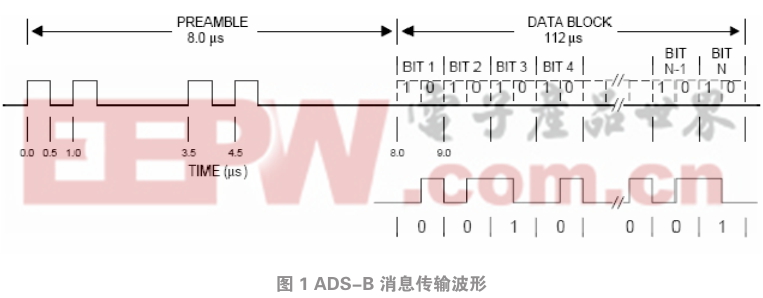

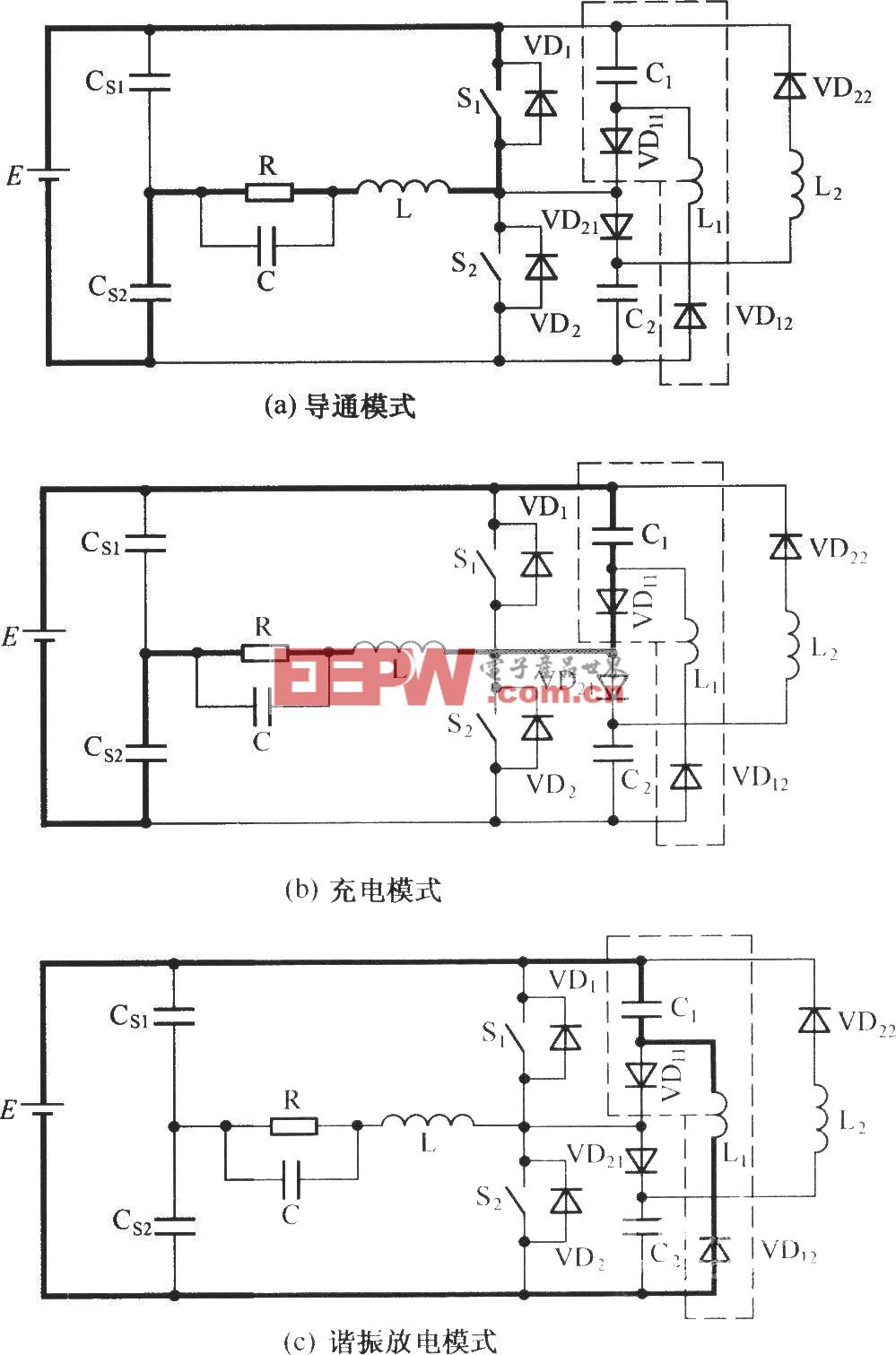

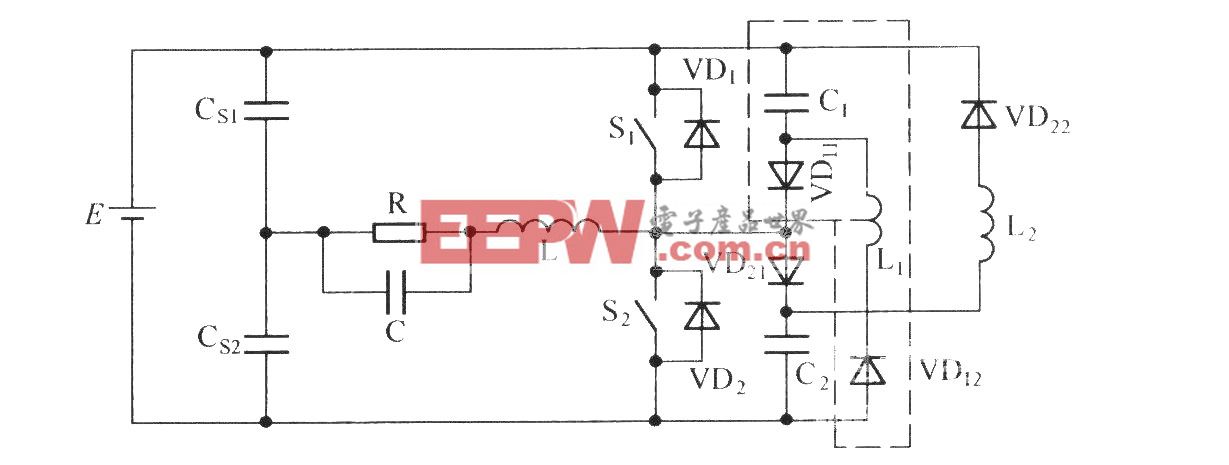

在SPI从模式下,设计使OMAP-L137、ADS1178作从片,CPLD作主片来提供进行数据传输的时钟。OMAP-L137的SPI接口支持3针、4针、5针三种传输模式,这里采用3针模式(即CLK、SIMO、SOMI)。OMAP- L137引出一个GPIO口作同步信号线SYCN,ADS1178的READY信号线送给CPLD用来产生采样时钟,硬件连接如图1所示。CLK用来传递接收和发送数据时的同步时钟信号,SIMO在OMAP-L137作主片时为输出数据线,在OMAP-L137作从片时为输人数据线。SOMI在此模式下不被采用。

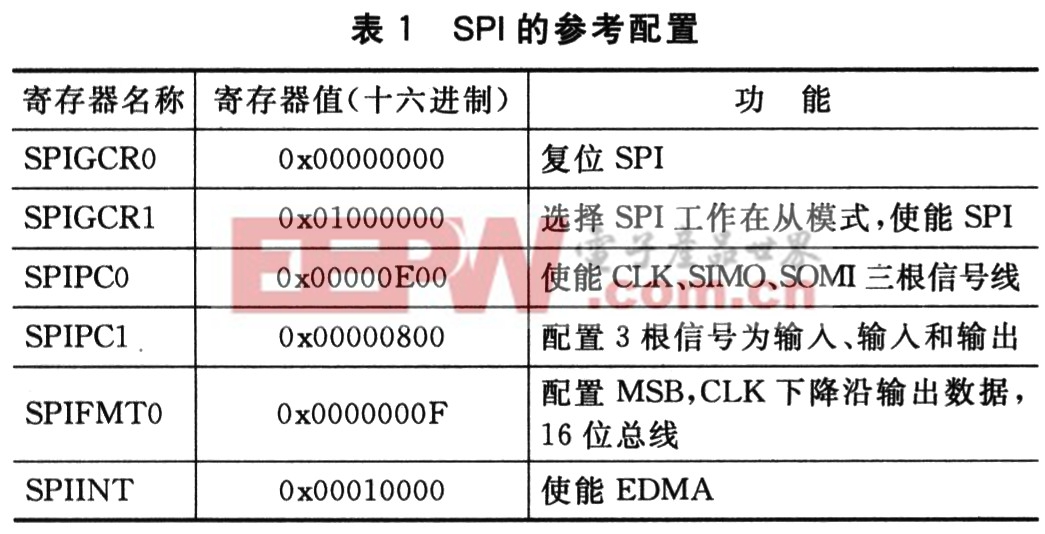

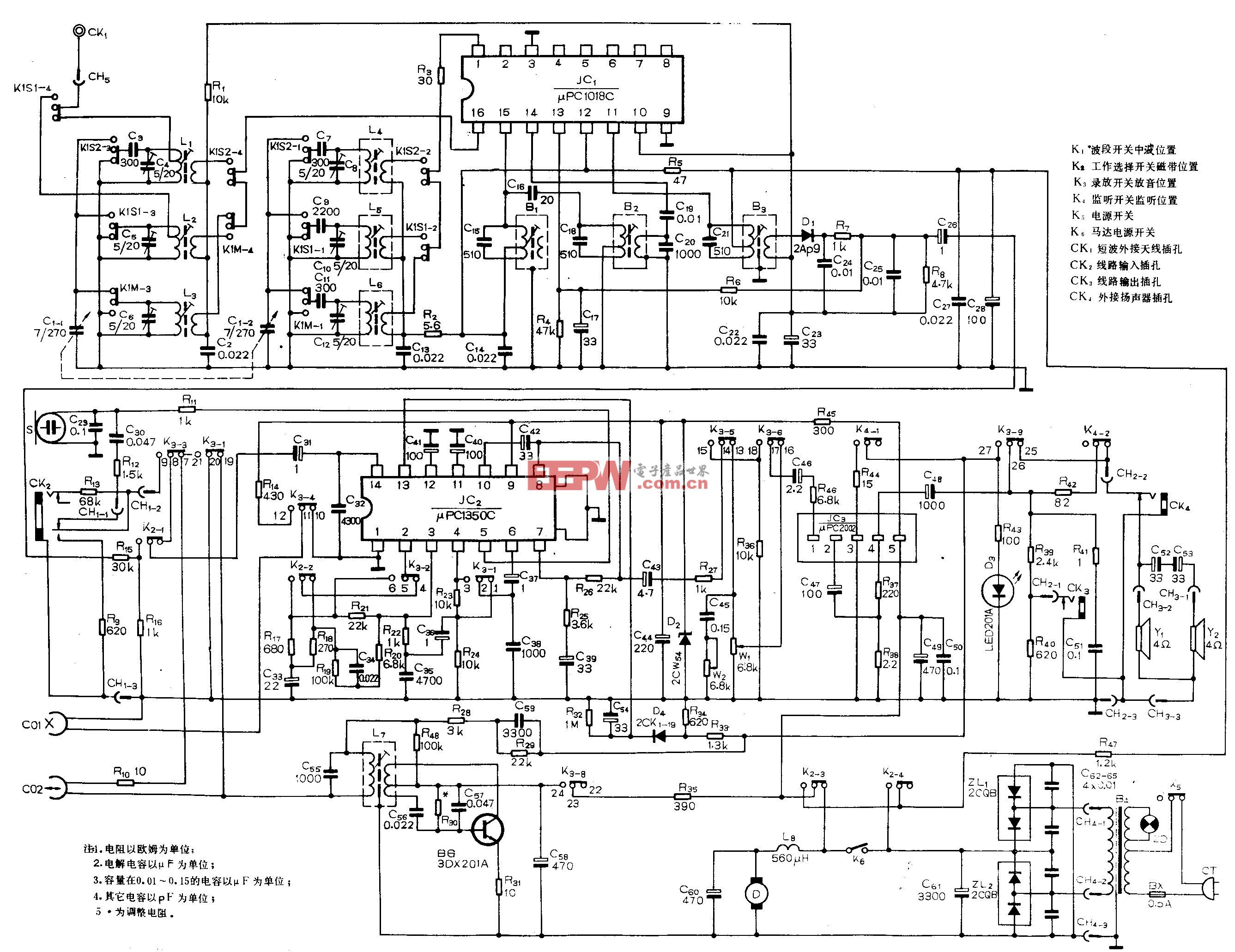

OMAP-L137的SPI接口工作在从模式的配置如下:SPIGCR1寄存器的低2位配置为00,选择SPI工作在从模式;通过配置SPIPC0和 SPIPC1寄存器来选择采用的针模式和引脚的信号方向,这里选择使能CLK、SIMO、SOMI三根信号线,并分别配置为输入、输入和输出;配置 SPIFMT0寄存器先输出每组数据的“大端MSB”,根据ADS1178手册中对数据输出时序的要求,配置数据在CLK信号的下降沿输出,使CLK信号工作在13MHz,同时配置现在的数据总线为16位。SPI的参考配置如表1所列。

在采样数据送到OMAP-L137的SPI接口时,可以启动EDMA模块来对采样数据进行搬移。EDMA的触发事件为SPI的每一通道数据(16位)的接收中断,相当于完成一组(8通道)数据的传输需要8个触发事件。EDMA的参数相关配置如图2所示。其中,OPT、DSTCINT、SRCCIND和 CCNT都需要根据应用情况来进行参数配置。

2 软件设计

2.1 CPLD程序设计

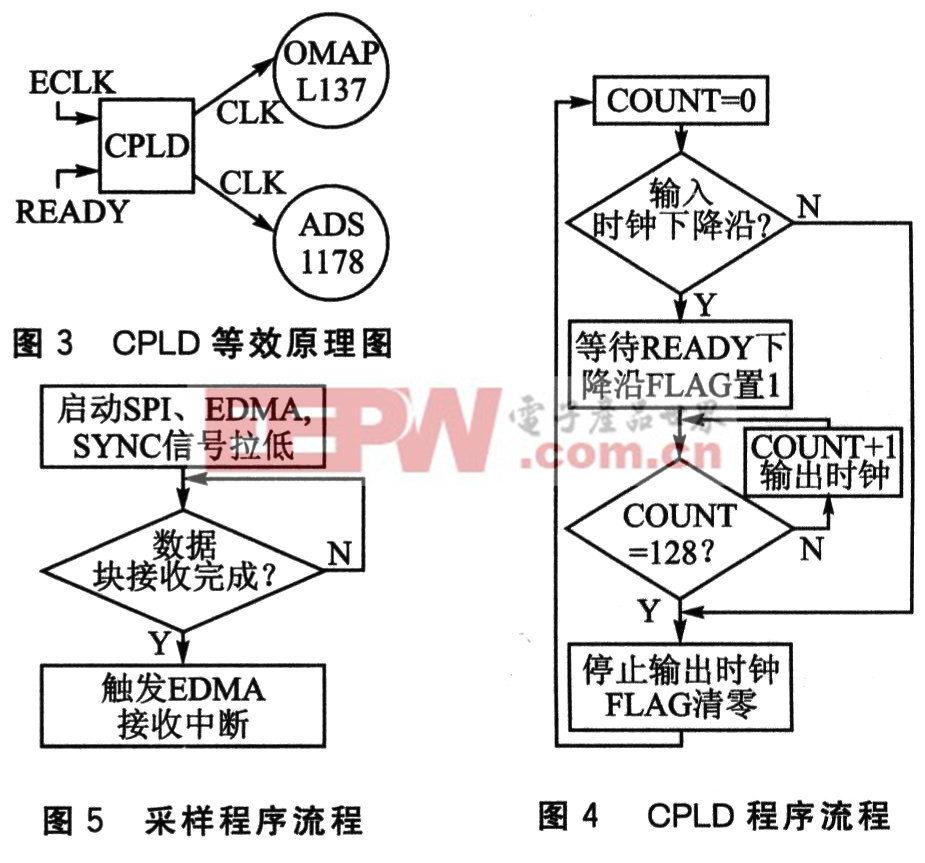

CPLD中主要实现ADS1178对数据格式的要求。在检测到READY信号的电平变化后,以外部时钟ECLK为时钟基准,产生128个时钟周期 (CLK)分别送给OMAP-L137和ADS1178,来完成8通道的数据传输。图3为等效原理图,CPLD程序流程如图4所示。

2.2 采样程序设计

代码调试中的主要工作是测试同步采样A/D的8路通道。SPI和EDMA的参考配置及使能在上面已经完成。当ADS1178开始数据采集时,通过GPIO口由OMAP-L137先向ADS1178发送一个由低变高的同步信号来通知 ADS1178开始工作。当ADS1178完成了数据转换时,向OMAP-L137发送一个由高到低的READ-Y信号,通知OMAP-L137数据已经准备就绪,等待主芯片的时钟将数据送到数据线上;并在CPLD送出采样时钟后,等待EDMA的数据接收中断,当中断到来时完成数据的采集工作。采样程序流程如图5所示。

评论