用中档FPGA实现高速DDR3存储器控制器

对于DDR3存储器读接口,当存储器件驱动DQS为低电平时,DQS转换检测块检测DQS的过渡情况,并生成读时钟来传输数据至FPGA。

莱迪思的IPexpress工具可用于生成上面阐述的DDR3存储器接口块。通过提供与高速DDR3存储器接口所需的合适块,这些在LatticeECP3中预制的块使设计人员减少了设计的复杂性。

DDR3存储器控制器

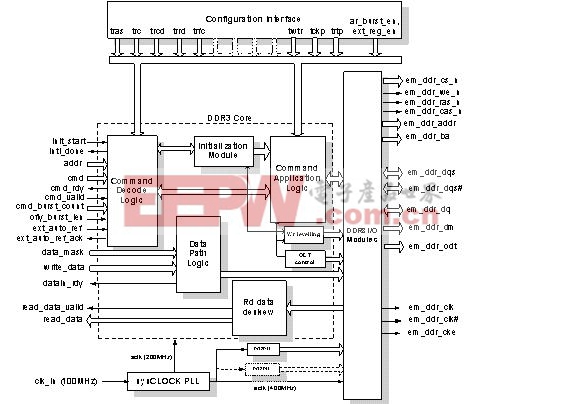

莱迪思提供一个全功能的DDR3存储器控制器IP核,接口至符合行业标准的DDR3元件和DIMM。莱迪思的DDR3存储器控制器的框图如图4所示。莱迪思的存储器控制器连接到LatticeECP3 的DDR3存储器接口模块(IO模块)和时钟电路,针对接口至DDR3存储器元件和DIMM,为客户提供现成的解决方案。这个控制器实现了一些功能,以改善整个吞吐量。例如,实现命令流水线,以改善整体吞吐量。该IP使用有效的分组(bank)管理技术来并行管理多个分组。这可以使访问延迟最小,有利于提高存储器的带宽。

使用莱迪思的IPexpress工具,可以生成LatticeECP3 的DDR3存储器控制器。基于GUI的工具使设计人员能够指定存储器控制器的参数(时钟频率、数据总线宽度、配置等)以生成DDR3存储器控制器IP核。设计人员可以通过图形用户界面定制参数。例如,图形用户界面允许用户定制存储器的时序参数,并用新的时序值重新生成存储器控制器。除了DDR3存储器控制器IP核之外,还提供仿真模型和测试平台,这样设计人员可以在将它按装到电路板上之前,对设计进行测试。

图4 莱迪思DDR3存储器控制器框图

LatticeECP3 DDR3存储器控制器已经用DDR3存储器元件和DIMM做了充分的验证。莱迪思还提供了多种硬件评估板,客户可用于检查LatticeECP3 DDR3存储器控制器的操作,接口至任何DIMM的 DDR3元件。LatticeECP3系列是业界唯一支持DDR3存储器接口的中档FPGA,从而针对下一代的系统设计,为设计人员提供了低成本,低功耗的解决方案。

结论

系统带宽的需求继续以指数形式增长。由于DDR3 SDRAM的价格下降了,DDR3 SDRAM芯片将更广泛地用于网络应用。这些增加系统带宽的要求正在推动着存储器的接口速度增加,同时继续使成本降低。用中档的FPGA促进稳定的高速存储器接口设计是LatticeECP3系列FPGA的主要目标。针对下一代存储器控制器的需要,ECP3的专用、灵活的DDR功能意味着现在设计人员有了一个节约成本的解决方案。LatticeECP3 DDR3基元与莱迪思的DDR3存储器控制器IP核的结合大大降低了DDR3存储器接口的复杂性,针对用DDR3实现下一代系统设计,促进更快地将产品推向市场。

评论