基于FPGA快速A 律压缩编码的设计与实现

3 编码流水线算法设计思路

本设计从适合流水线操作的角度对常规算法[5]作了改进,前级完成相应位计算后将其结果传递到下一级,完成后进入下一组数据的编码运算,从而达到流水作业的目的。由于每个模块功能独立,适合模块化设计。

4 具体实现

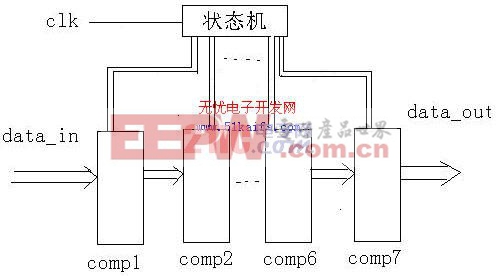

图2 系统框图

图2系统框图中实现了一种并行数据处理且适合于编码流水线作业的改进算法,并采用FPGA具体实现。系统主要由状态机(state)和比较单元(compare)这二部分组成,其中Comp1,Comp2,……Comp7这七个单元模块在状态机的控制下并行进行流水线数据处理。即在状态机的控制下,在一个clk时钟脉冲当中,七个单元同时进行着数据的处理工作,处理完成后,前一个Comp单元的输出作为后一个Comp单元输入,在下一个clk时钟脉冲到来时紧接着又进行下一组数据处理。按照这种方式,依次处理下去,从而达到流水线作业的目的。下面对该系统进行具体实现。

评论