基于FPGA的∑-Δ D/A转换器的设计与实现

作为例子,本文中所描述的∑-Δ DAC的二进制8位输入数字量是无符号数,模拟输出电压值都是正值。输入“00000000”产生输出电压0V,“11111111”产生输出电压的最大值Vmax,Vmax非常接近VCCO,其中VCCO是FPGA芯片I/O端口的供电电压。本文引用地址:http://www.eepw.com.cn/article/191733.htm

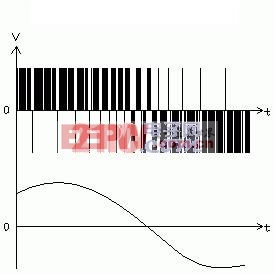

图1 脉冲密度调制

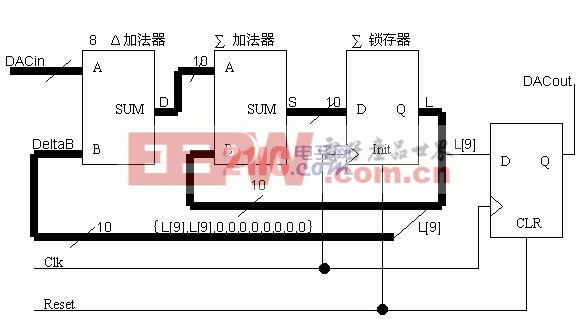

图2 ∑-Δ DAC的内部结构图

术语“∑-Δ”分别代表算术和与差,都可用二进制加法器来产生。虽然Δ加法器的输入是无符号数,但Δ和∑两加法器的输出被看作有符号数。Δ加法器用来计算DAC输入与当前DAC输出之间的差值。由于DAC的输出只有一位,非0即1,即全0或全1。如图2 ∑-Δ DAC的结构图所示,Δ加法器的另一个输入值由∑锁存器最高位L[9]的两个拷贝后面跟8个0产生,这也弥补了DAC输入值是无符号数的问题。∑加法器将它的上一次输出(已经保存在∑锁存器)与Δ加法器的当前输出求和。

3∑-Δ DAC的FPGA实现

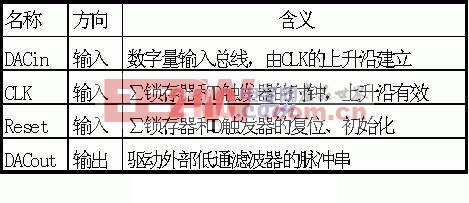

如图2所示,∑-Δ DAC的内部仅由2个10位的二进制加法器,1个10位的锁存器和一个D触发器组成,用FPGA实现时只需耗费极少的逻辑资源,即使用最小的FPGA也能实现,本文采用了Xilinx Virtex FPGA,图3给出了FPGA实现的顶层原理图。输入信号有8位宽的二进制数字量DACin[7:0]、时钟信号CLK和复位信号Reset;输出信号为等幅脉冲串DACout,通过一个驱动缓冲器OBUF_F_24(是Xilinx FPGA特有的SelectI/O资源,OBUF表示输出缓冲器,F表示它的转换速率快,24表示它的驱动能力即输出驱动电流是24MA,基于LVTTL I/O标准)驱动FPGA外部的模拟RC低通滤波器,该缓冲器的输出端连接到FPGA的I/O端口,则它的驱动电压即为FPGA的I/O端口的供电电压VCCO。表1列出了∑-Δ DAC的接口信号。

图3 FPGA实现∑-Δ DAC的顶层原理图

表1 ∑-Δ DAC的接口信号

评论