多路接口与E1协议转换器设计与实现

2 关键模块设计

2.1 与CPU通信FPGA端硬件电路设计

当FPGA与CPU通信时,由于CPU总线特殊的时序关系,FPGA端须做相应的处理才能保证读写数据的稳定性。图3为MPC875读数据总线时序图。其中:本文引用地址:http://www.eepw.com.cn/article/191187.htm

当CPU读取FPGA中数据时,先给出地址信号,然后使能片选![]() 、读信号

、读信号![]() ,这时如果数据总线上有数据,CPU读入数据。但MPC875总线频率高达80 MHz,为了CPU能稳定的读取到数据,这里将片选信号与读信号相“与”,然后扩宽3倍得到总线可用信号,在总线可用信号有效期间,数据总线上总有数据,这样,可以保证CPU能稳定的读到数据。

,这时如果数据总线上有数据,CPU读入数据。但MPC875总线频率高达80 MHz,为了CPU能稳定的读取到数据,这里将片选信号与读信号相“与”,然后扩宽3倍得到总线可用信号,在总线可用信号有效期间,数据总线上总有数据,这样,可以保证CPU能稳定的读到数据。

当CPU写入数据时,CPU先给出地址信号,然后给出片选及写信号,在写信号有效期间,CPU稳定的给出数据。因此,在片选及写信号有效时,锁存数据总线上的数据即可。

2.2 CPLD硬件接口电路设计

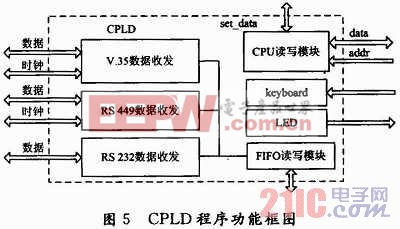

CPLD主要完成V.35,RS 449,RS 232数据收发;keyboard,LED控制;FIFO读写等功能。功能框图如图5所示。

CPU通过CPLD对接口芯片进行模式选择。V.35,RS 449为同步平衡接口,常用接口速率为N×64 Kb/s(N=1~32)。时钟、数据信号为两线平衡传输,控制信号为不平衡传输。发送数据时,将与之对应的时钟一并输出。在接收数据时,用接口时钟采样数据。

RS 232为不平衡传输。帧格式固定为:1位开始位、8位数据位、结束位。结束位有三种:1位、1.5位、2位。开始位固定为“0”,停止位固定为“1”。通信双方在开始通信前必须约定好串行传输的参数(传输速度、帧格式)。在发送端,首先通过分频产生需要的串行波特率,然后按照帧格式以约定好的速率发送。在接收端,使用8倍于波特率的时钟对接收到的信号进行过采样,经过滤波后如果为低电平信号,即认为是开始位,然后按照约定好的速率接收数据。

在接收数据时,FIFO读写模块将串行接收数据变成8位并行,同时,将与接收数据同步的时钟8分频,用此时钟将8位并行数据写入与该接口对应的FIFO;在发送数据时,将发送时钟8分频,用此时钟从与该接口对应的FIFO读取数据,同时将8位并行数据串行输出。

keyboard为4×4扫描式矩阵键盘,具有16个键。由硬件程序自动扫描键盘,输入数据触发中断,CPU读取数据。LED输出由CPU写入相应的显示寄存器,然后硬件程序将相关信号输出点亮LED。

2.3 FPGA硬件电路设计

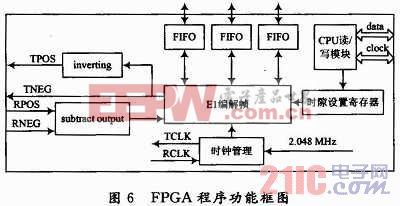

FPGA主要根据时隙的分配设置,在时钟系统的管理控制下,完成E1的编解帧功能。功能框图如图6所示。

CPU根据设置向时隙分配寄存器写入相应的数据。在发送数据时,E1编解帧模块根据时隙分配设置,从相应的FIFO读取数据,写入该时隙。对于没有使用的空时隙,按照空时隙处理办法填入无效数据。发送时钟为FPGA外接的2.048 MHz时钟。由于XRT82D20为数据差分输入,因此将编解帧模块输出的数据TPOS进行反向得到TNEG,平衡输出。TCLK为发送时钟。

在接收时,XRT82D20数据差分输入RPOS,RNEG,将两个信号相减得到输入数据信号,RCLK为时钟输入。在输入时钟的控制下,E1编解帧模块将数据解帧。同时,根据时隙分配设置,将各个时隙的数据送入不同的接口FIFO。

评论