基于FPGA+DSP导引头信号处理中FPGA设计的关键技术

3.2.1 三态门的设计

在本设计中,DSP和FPGA的互连采用了总线连接的方式,数据交互是通过一个32位的双向数据总线来完成的,而要实现双向总线,就需要使用FPGA构造三态总线了,使用三态缓冲器实现高、低电平和高阻三个状态。

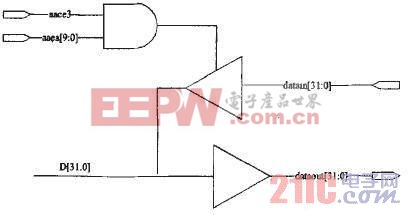

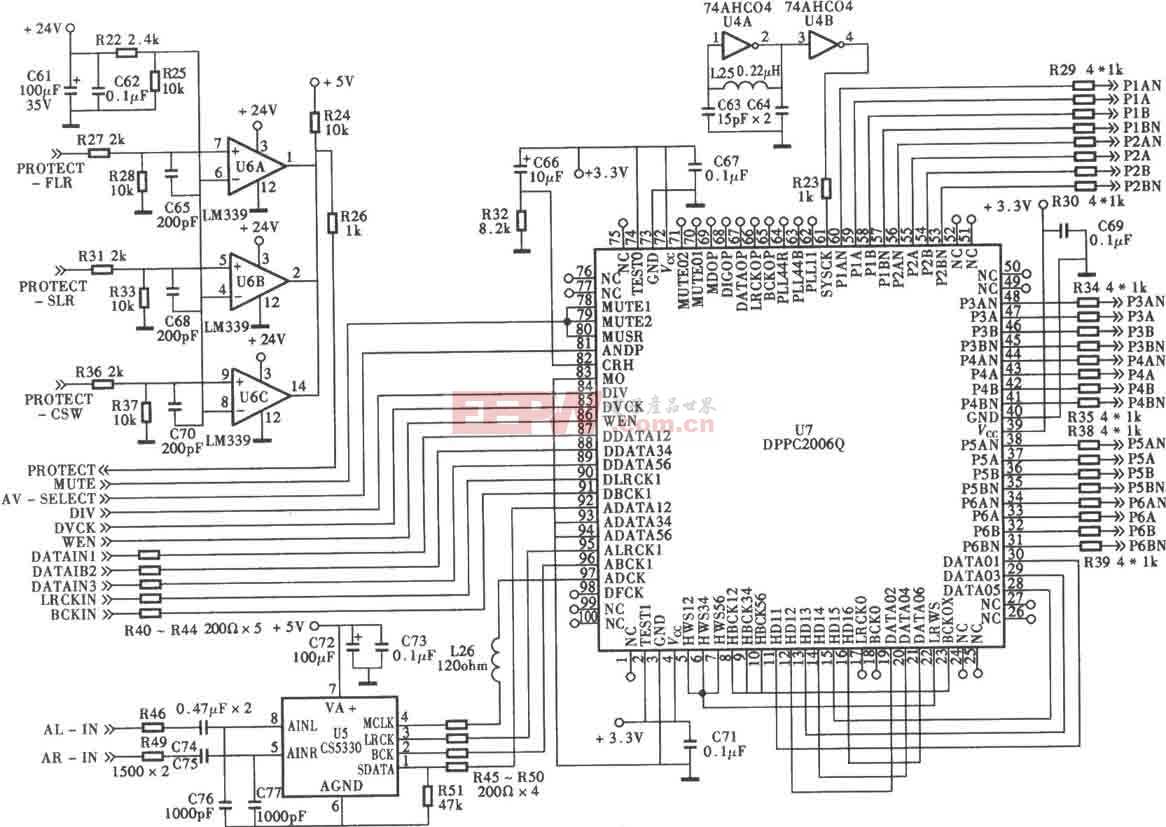

图5双向数据总线的三态门设计

本设计当中,FPGA给DSP发中断信号,DSP在中断信号到来时,根据系统要求,将不同的控制字写入数据总线,然后通过数据总线从FPGA中不同的FIFO中读取数据,这一切都通过DSP在地址线上给出不同的地址来完成。为了合理分配总线的使用,设计当中使用这样的策略:利用片选信号aace3,地址aaea[9:0]作为三态缓冲器的控制信号,由于DSP对FPGA的读写地址都不同,当片选信号aace3有效时,FPGA根据地址来确定凑写方式以及读写那些信息,否则置为高阻态,这样就避免了可能产生的的总线阻塞现象,使DSP和FPGA之间的数据交互能够顺利进行,示意图如图5所示。

3.2.2 加有效的时序约束

由于接口FIFO比较多,为了合理分配FPGA内部接口处的资源,满足系统的时序要求,需要加必要的时序约束。因为本设计采用Xilinx公司芯片,所以需要加偏移约束2。

偏置约束可以优化以下时延路径:从输入管脚到同步元件偏置输入;从同步元件到输出管脚偏置输出。为了确保芯片数据采样可靠和下级芯片之间正确交换数据,需要约束外部时钟和数据输入输出引脚问的时序关系。偏置约束的内容告诉综合器,布线器输入数据到达的时刻或者输出数据稳定的时刻,从而保证与下一级电路的时序关系。更多关于约束的内容请参阅文献。

4 结束语

FPGA+DSP是同前导引头信号处理器中运用的最广泛的系统组成形式,对速度以及灵活性的要求都能够很好的满足,文中所涉及到的跨时钟域设计以及数据接口方面的问题是这样的系统中FPGA设计存在的关键技术,文中提出了详实的解决方法,而且工程应用已经证明了其有效性。

本文作者创新点:依据工程实践经验,总结了在FPGA+DSP结构的雷达导引头信号处理中FPGA的关键问题,并提出了详细的解决方案,并得到了工程验证。

评论