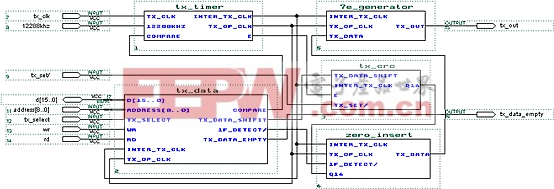

图3

待发送数据是由外部CPU通过interface模块写入指定地址的缓冲存储器的。在HDLC中,可以选用的缓冲存储器类型有FIFO(先进先出)存储器、DPRAM(双端口RAM)存储器、移位寄存器等。在本设计中,发送数据的存储使用的是数据锁存移位寄存器。使用这种寄存器的优点是:写入的待发送数据经锁存后,可在任何时候(包括正在发送时)对数据的任何部分读出检查,并且数据可直接串行移位做CRC计算,简化FPGA设计。这种寄存器由数据锁存器和串行移位寄存器两部分组成,占用芯片资源较多,但对于有大量片上存储器可用的FPGA 芯片来说,这点是不成问题的。

评论