基于FPGA的高速数据采集控制模块设计

FPGA收到的10位并行数据,经过10B/8B解码、数据判断、帧提取后得到12 MHz速率的数据帧。根据系统通信协议,取出数据帧的一部分缓存入双口RAM作为采集数据的帧头。数据帧第2个Byte的第3位确定采样频率,当其为1时采样频率为20 MHz,当其为0时采样频率为2MHz。FP GA接收到上位机发送的采样导前信号后将帧头以60 MHz速率缓存,当采样时间长度信号到来后按照所需的采样频率开始进行采样,同样以60 MHz速率缓存。然后将帧头和采集数据经过组帧、8B/10B编码后发送出去。本文引用地址:http://www.eepw.com.cn/article/190186.htm

图4为经光纤收到的数据在解码后的处理结果。其中clk12为12 MHz的时钟;dina为解码后的数据帧;st与数据帧的第1个Byte对齐,方便后续编程工作的进行。由于数据帧的第2个Byte AE的第3位为1,所以采样频率为20 MHz。

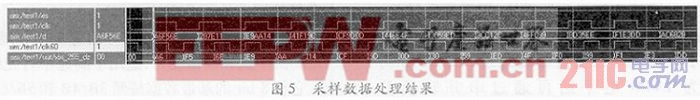

图5为采样数据处理结果。其中es为采样时间长度信号;clk为40 MHz的时钟;d为40 MHz采样数据;clk60为60 MHz时钟;dz为d经20 MHz采样,转换为3个Byte后的数据。例如示例中d为A6F56E,287E11,E9AA14,41F19C,CF9D0D,448E4F等,dz取其中的隔项,如:A6F56E,E9AA14,CF、9DOD等,将每项转换为3 Byte,如A6,F5,6E,E9,AA,14,CF,9D,0D等。

4 结束语

文中所设计的高速数据采集控制模块以FPGA为核心,配以信号调理、模数转换、光收发模块等电路,实现了高速数据采集和光纤传输。该模块具有精度高,处理速度快,实时性好等特点,已经成功应用于某项目中,经试验验证,完全满足系统对信号采集和处理的实际要求。

评论