端接电路的串扰详细介绍

本文引用地址:http://www.eepw.com.cn/article/190126.htm

如果电阻的布局是交错的,如图6.18所示,就要用交叠长度来代替上式中的Y。

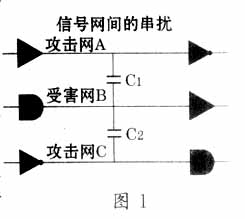

2、相邻表面贴装电阻的串扰

表面贴装电阻本身距离电路板比较近,与实芯电阻相比,可以大大降低串扰系数。为了取得最好的效果,使地平面层接近电路板外层表面,直接把地层埋在表面贴装元件下面,这样可以减小上式中的参数H、降低串扰。

3、单列直插(SIP)端接电阻的串据

这些器件的效果可能好,也可能不好,这要取决于其内部的走线。图6.19显示出了单接地引脚端接电阻的共同电流路径,这个共同电流路径会在该封装的电阻间引入大量的耦合电感。

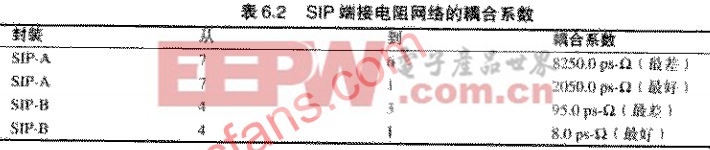

表6.2列出了0.1IN间距SIP封装电阻排的典型耦合系数。封装SIP-A包含7个电阻,采用8引脚的封装,一端有公共的地线引脚。在封装SIP-A中,电阻7距离地线引脚最远,封装SIP-B包含4个电阻,采用8引脚的封装,每个电阻都有独立的地,所有的电阻都是50欧,独立SIP-B封装比公共地网络的性能几乎好100倍。

采用式 可以把这些耦合系数转换成耦合噪声电平。

可以把这些耦合系数转换成耦合噪声电平。

评论