基于Virtex-6 FPGA的双缓冲模式PCIe总线设计方案和

3.2 PCIE核配置

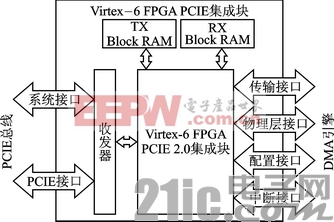

Virtex6 PCIE Endpoint Block[4]集成了传输层(TL)、数据链路层(DLL)和物理层(PL)协议,它完全符合PCIE基本规范,可配置性增加了设计的灵活性,降低了成本。其功能框图与接口如图5所示。其中收发器通过PCIE总线与Root Complex实现数据包的传递,PCIE总线由系统接口和PCIE接口组成;系统接口由复位和时钟信号组成,PCIE接口由8条差分传输和接收对组成(8lane)。TX/RX Block RAM用来存储来自DMA引擎和系统内存的数据,其大小可以通过Xilinx Core Generator配置。传输接口为用户提供了产生和接收TLP的机制;物理层接口使用户能够观测和控制链路的状态;配置接口使用户能够观察和配置PCIE终端的配置空间,即DMA寄存器;中断接口实现DMA与PCIE核之间的中断传输。用户通过这些接口设计符合其需要的DMA引擎。

图5 PCIE功能框图与接口

本文使用Xilinx CORE Generator生成PCIE核,其主要配置参数如表1所列。

表1 PCIE核主要配置参数

3.3 总线主控DMA传输

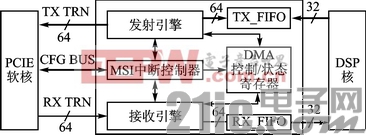

参考Xilinx应用实例XAPP1052[5],本文设计的DMA结构框图如图6所示,各部分功能介绍如下:

①发射引擎。发射引擎产生传输层数据包(TLP)并通过传输接口发送至PCIE核,数据包的数据来自TX_FIFO,头信息来自DMA控制/状态寄存器,也负责驱动对DMA寄存器的读取。

②接收引擎。接收引擎将来自上位机的数据包解码并转存至RX_FIFO中,也接收来自驱动的配置信息并将寄存器值写入DMA控制/状态寄存器中。

③DMA控制/状态寄存器。该模块是DMA的主控制器,控制着DMA复位、读写等操作;内存缓冲区的地址信息和TLP包长度等信息也存储在该寄存器中。

④MSI中断控制器。该模块产生读写中断,然后通过中断接口通知PCIE核,进而通知驱动程序。

⑤TX/RX_FIFO.通过Xilinx Core Generator将FIFO配置为独立时钟异步模式,实现不同时钟域的数据缓冲和位宽转换。本文PCIE时钟为250 MHz、位宽64位,而DSP核时钟为200 MHz、位宽32位。

⑥PCIE核。该模块为例化的PCIE集成块,框图和参数详见图5和表1.

⑦DSP核。该模块为用户设计的算法或者功能模块,例如通过Simulink调用Xilinx库实现某种功能。

图6 DMA结构框图

评论