基于FPGA的PCI数据采集卡设计

2.2.1 总线读写设计

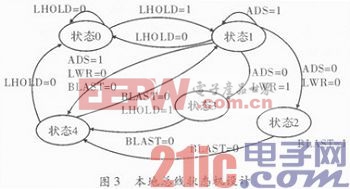

总线读写设计是FPGA设计的顶层模块,主要完成PCI9054与本地的通信,实现数据的正确传输。PCI9054单周期读、写和DMA读的VHDL语言时序控制状态机如图3所示。状态0为空闲状态,状态1为总线保持状态,状态2为DMA读状态,状态3为单周期写状态,状态4为读写操作完成状态。本文引用地址:http://www.eepw.com.cn/article/189530.htm

2.2.2 控制信号说明

ADS#:地址选通信号,双向。表示地址有效及新的总线访问周期的开始,在总线访问周围的第一个时钟周期有效。BLAST#:突发传输结束信号,双向。由当前本地总线主动方驱动,用来表明总线传输的最后一个数据传输。LW/R#:写/读信号,双向。低位读,高为写。LHOL D:保持总线请求,输出。请求使用本地总线。当控制可以实现时,本地总线仲裁回应LHOLDA。

2.2.3 A/D控制设计

A/D控制是数据采集卡的主要部分,设计主要包括:A/D采样时钟的产生,分组采集控制,触发设置及FIFO读写控制等。

(1)A/D采样时钟的产生。采样时钟的产生主要是根据设定的采样频率产生具有一定低脉宽的信号,这是为了在转换完成时能正确地读出转换数据。值得注意的是,在FIFO溢出的情况下及分组采集的组间间隔时间段内要停止输出采集脉冲。

(2)分组采集控制。分组采集是按照内外时钟源分别进行设计的。首先根据组循环次数及首末通道设置计算出一组内总共要采集的点数,即:一组内总共要采集的点数=(末通道-首通道+1)*组循环次数。

在内时钟模式下,启动A/D转换后,在每次转换完成后采集点数加1,直至加到一组内总共要采集点数为止,此时停止输出转换脉冲,而后进入组问间隔时间,开始对基准时钟进行计数,计到设定的组间间隔值后输出转换脉冲,再次进入转换计数周期,依此重复下去。

在外时钟模式下,当检测到外时钟下降沿时开始输出转换脉冲并在转换完成后进行计数,直至加到一组内总共要采集的点数为止,此时停止输出转换脉冲,当再次出现外时钟的下降沿时,便开始新的一组分组采集。

(3)触发设置。触发设置是根据板卡控制字中的触发源、触发方向及触发类型共同决定的。

(4)FIFO读写控制。FIFO的读是由PCI9054发起的,在PCI9054读周期,在满足地址条件的情况下,产生FIFO的读信号,将A/D数据传输到主机。

FIFO的写信号是由A/D芯片的STS信号控制的,当STS信号由高变为低时表示本次转换完成,且数据线上数据有效,而FIFO是在下降沿启动写周期,上升沿将数据打入FIFO中,因此只需将STS信号取反后赋给FIFO的写信号。

3 硬件设计的测试

在板卡的设计过程中,硬件设计的测试是按如下步骤进行的:首先通过功能仿真及时序仿真排除设计上的大部分错误;其次通过PCItr ee软件进行测试,通过简单的功能测试,如开关量输入输出;然后通过简易演示程序测试;最后通过高级程序的全面测试。在不同的测试阶段会发现各种设计问题,再将设计回归到功能仿真及时序仿真,反复修改完善程序,直到最终满足功能设计要求。

4 结束语

本文完成了基于FPGA的PCI数据采集卡的设计,板卡实现了查询、中断和DMA等多种方式读取数据,可实时采集数据,实现大容量数据的缓存,有效地解决对数据高速采集和传输的需求。可直接插在PC机或与之兼容的计算机内任一PCI插槽中,构成各领域的数据采集、波形分析和处理系统,也可构成工业生产过程监控系统。

fpga相关文章:fpga是什么

评论