FPGA实现FIR抽取滤波器的设计

3 滤波器系数的求取

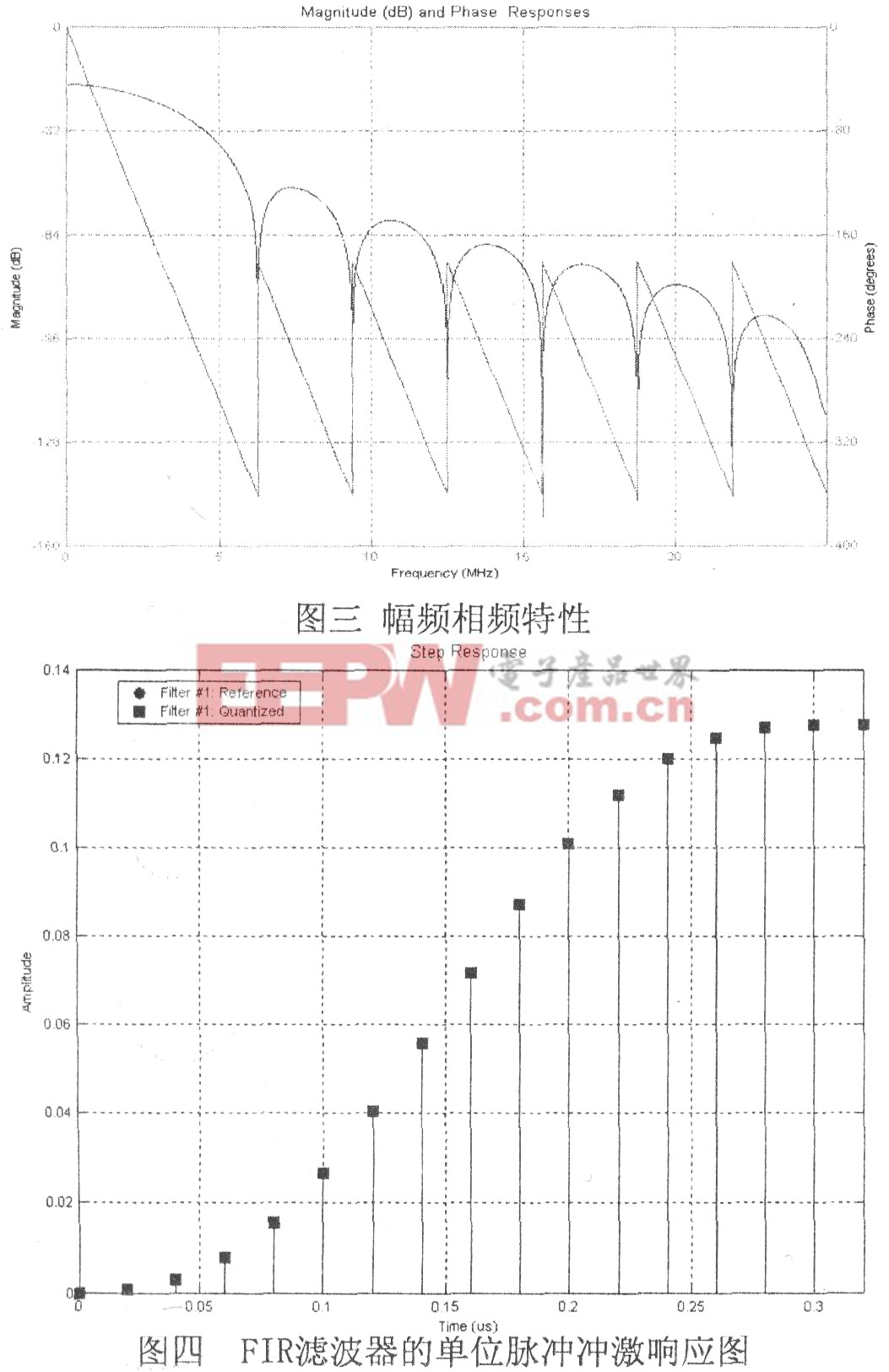

使用Matlab集成的滤波器设计工具FDAtool,可以完成多种滤波器的数值设计、分析与评估,设计16阶低通滤波器参数如下:

采样频率:Fs为50MHz,滤波器归一化截止频率:Fc为0.4MHz,输入数据位宽:8位,输出数据宽度:16位FDAtool采用汉宁窗函数(Hanning)设计16阶线性相位FIR数字滤波器,并提取其特性参数h(n)浮点数值。本文引用地址:http://www.eepw.com.cn/article/188940.htm

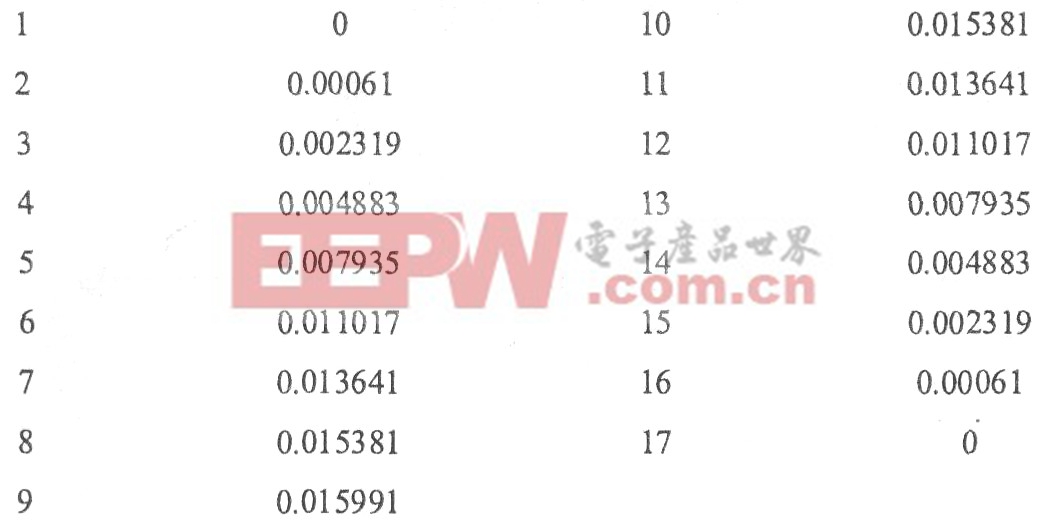

MATLAB中算出的系数h(n)的值是一组浮点数,进行浮点值到定点值的转换,用16位二进制补码表示为

滤波器抽头数是16个,考虑到线性FIR滤波器的偶对称特性,只考虑8个独立滤波器抽头数,则需要一个28×8的表(其中指数8指的是8个滤波器抽头数,后面的8指的是输入数据的位宽)。但是Virrex―e FPGA只能提供4输入的杏找表,所以要对查找表的地址进行电路分割。将8位地址线分为高4位和低4位,分别作为两个24×8的查找表的地址输入,从而指数倍地节省了硬件资源。

4 主程序及仿真

在时钟和计数器的控制下,根据查找表输出结果位权的不同,将输入数据向左移动相应的位数,低位按照位权的不同补上个数相当的“0”,然后将移位数据进行累加操作,输出最终滤波结果,这里的结果依旧是用二进制数据表示的,只是位数因为移位和累加操作增加了8位。

评论