基于FPGA IP核的FFT实现

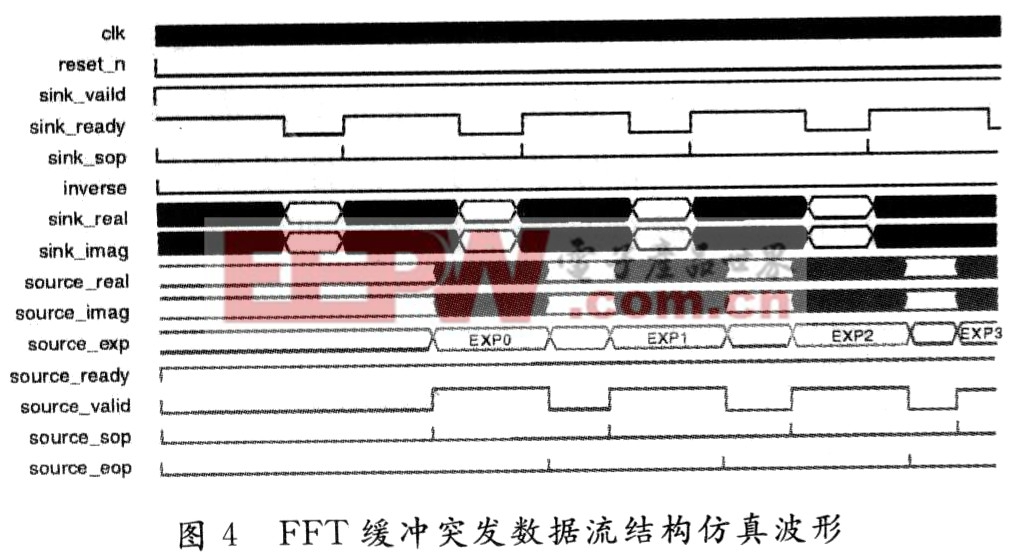

FFT处理器模块采用缓冲突发数据流结构的信号时序图如图4所示,在系统复位信号(reset_n)变为低电平后,数据源将sink_ready信号置高电平,表明有能力接收输入信号。数据源加载第一个复数数据样点到FFT函数中,同时将sink_sop信号置高电平,表示输入模块的开始。在下一个时钟周期,sink_sop信号被复位,并以自然顺序加载后面的N-1个复输人数据样点。

当完全载入输入模块时,FFT函数复位sink_ena信号,表示FFT不再接收其他输入数据并开始计算输入数据模块的变换结果。在FFT处理器内部输入缓冲区读取样点之后,FFT将sink_ena信号重新置高电平,准备读取下一个输入模块。下一个输入模块的起点由sink_sop脉冲确定。当FFT完成了输入模块的变换,并且从设备汇端将source_ready信号(表示数据从设备接收器可以接收输出数据模块)置高电平,并且以自然顺序输出复数变换域数据模块。

4.2 仿真结果分析

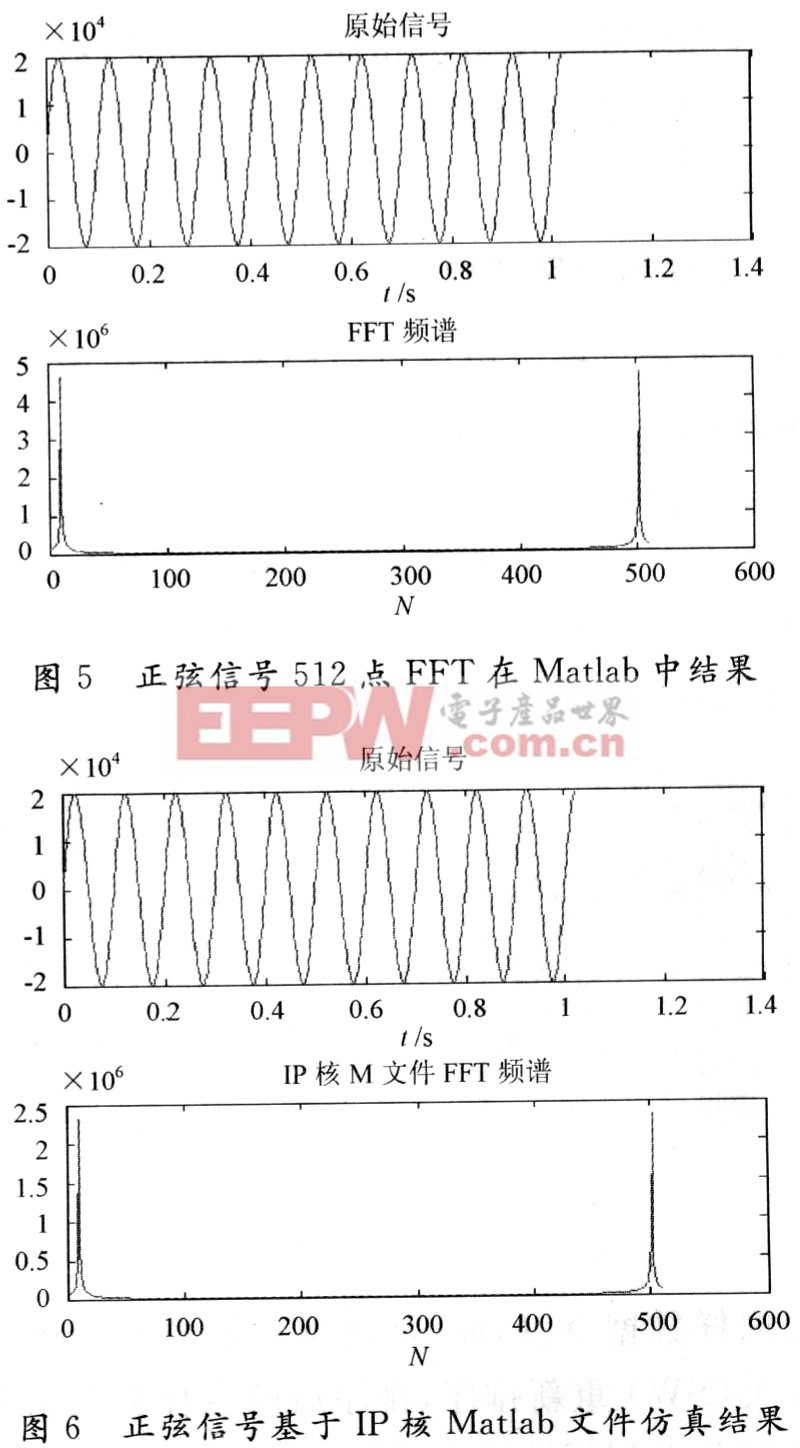

在编译综合后,工程当中含有基于FFT IP核生成的Matlab文件,这样就可在Matlab下对工程结果进行进一步测试,构建信号,并与Matlab计算的理论结果进行比较。设输入函数为z(t)=20 000sin(20πt),点数N=512,采样频率为500 Hz,即采样间隔为O.002 s,采样的时间长度为O.002 x 512 s,该正弦信号通过512点FFT处理结果如图5所示,正弦信号基于IP核Matlab文件仿真结果如图6所示。

由图5,图6比较可以看出FFT、处理器处理后的结果和Matlab计算的理论结果基本一致。都在第11点和第503点取得最大FFT绝对值,两者的误差只是在FFT频谱绝对值的幅度大小原因:一是Altera FFT兆核函数的块浮点输出与Matlab这种全精度FFT的输出相比,存在最低位(LSB)被丢弃的影响;二是工程初始化IP核采用的数据精度取24位(V7.0 IP最大支持24位数据精度)。

5 结 语

在利用FFT IP核进行FFT算法实现的同时,对仿真结果做了全面分析,由于IP核的可塑性很强,增加了芯片的灵活性。使用Altera FFT的IP Core大大减少了产品的开发时间,Altera还可进一步实现加窗功能,甚至DDC部分(单端信号向I/Q转换)整合到其FFT处理器模块中,能进一层次简化开发的流程,在今后实际工程应用中高效利用。

fpga相关文章:fpga是什么

评论