宽带CDMA发射机低相噪本振源的设计

CDMA及码分多址接入,是一种基于扩展频谱通信技术的多址接入方式。它采用唯一的码字将消息信号扩展到相对更宽的频带上,从而减少干扰,增强系统处理能力,并且可以区分用户。CDMA多址接入不要求分割频率和时间,因而系统容量较高。目前国际上主流的第三代移动通信技术(WCDMA,CDMA2000以及我国提出的TD-SCDMA)都采用了CDMA技术。CDMA收发信机将成为今后通信产品的主流。

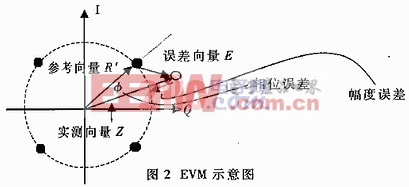

本文引用地址:http://www.eepw.com.cn/article/188081.htm本振源作为CDMA发射机心脏,对通信质量有着举足轻重的影响。CDMA技术对线性度和调制精度有严格的要求,因此,如何根据整机指标(如:误差向量幅度-EVM,邻道功率抑制比-ACPR),尤其是对本振源要求较高的多模手机,确定本振源可实现的具体指标(相位噪声等),并对电路进行设计与优化,成为各类CDMA通信设备设计者的新的挑战。

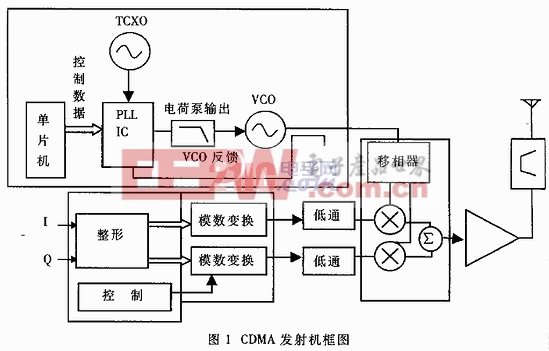

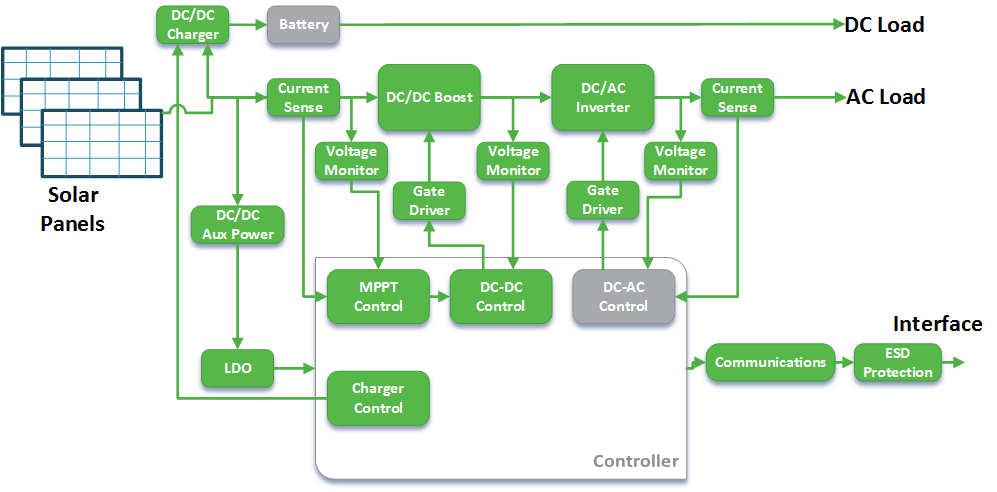

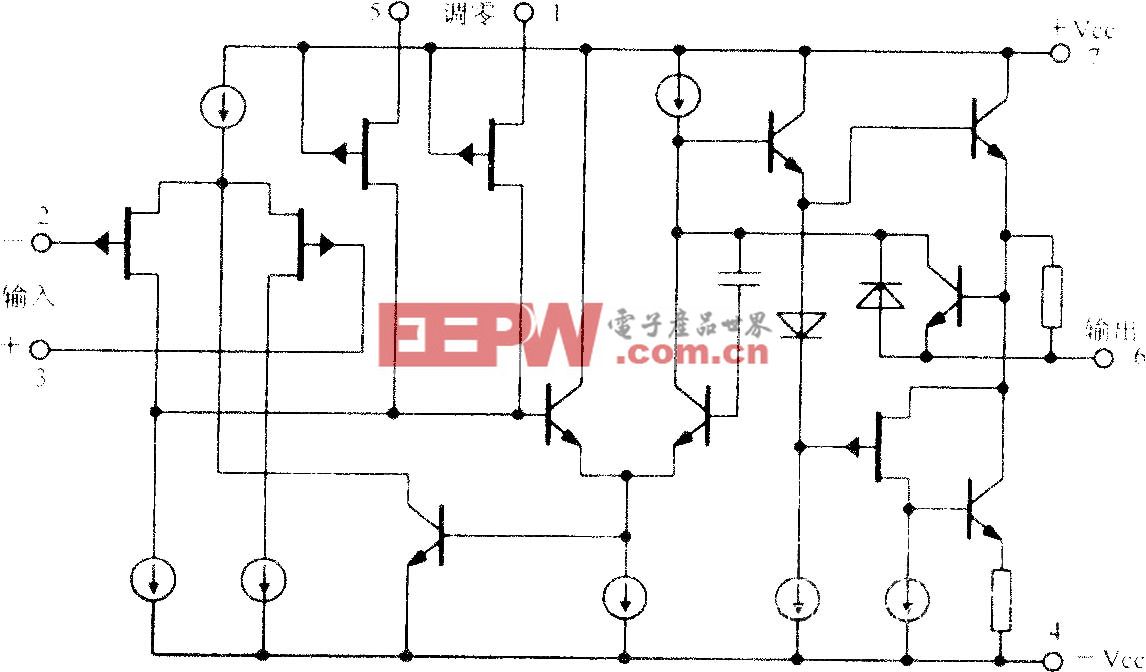

图1 CDMA发射机框图

本文介绍一款宽带CDMA发射机的本振源设计过程,提供一整套针对CDMA发射机本振电路(锁相环路)进行的电路指标确定、器件选取与参数设定以及电路设计的方案的可行性评估。

另外,对发射机系统的EVM指标进行了仿真,从而得出了合理的本振源相位误差指标。为便于设计者对锁相环路的优化与仿真,笔者还编写了一套ADS锁相环路仿真程序,不同于常见的优化和计算在后台进行的辅助程序。在使用本仿真程序时,设计得可以调整任意参数或器件值并迅速获得与该调整相应的所有关键指标(如:相噪、杂散、稳定性)的变化。

1 原理简介

宽带CDMA发射机框图如图1所示,其中左上部分为本振源电路。单片机通过数据部控制锁相环路芯片(PLL IC)使得该电路可以锁定在不同的信道上;温补晶振(TCXO)为锁相环路提供精确的参考频率源;压控振荡器(VCO)反馈信号与该频率源在PLL IC内进行鉴相。鉴相输出通过电荷泵和环路滤波器输出到压控振荡器的控制端控制其输出频率。

2 指标设定

与本振源相关的主要整机指标有:

・频稳度:±2×10 -6;

・EVM:15%;

・带宽:2.5MHz;

・ACPR:-40dB/±2.5MHz。

基于上述指标,得出以下针对本振源的一些具体指标:

(1)参考频率源频稳定:±1.7ppm(包括温度频稳度、供电电压频稳度、负载牵引频稳定和年老化率累加)。

cdma相关文章:cdma原理

评论