计数器应用实例

图5.3.36 图5.3.34电路的改进

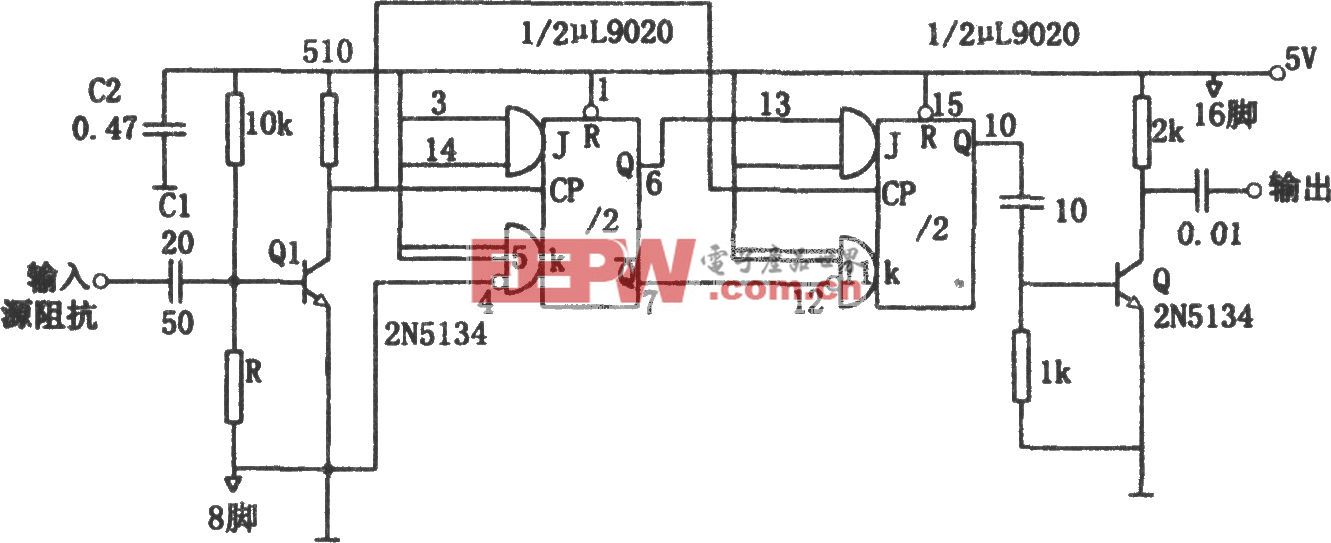

两个与非门构成了RS锁存器,以它的![]() 端输出的低电平作为74LS160的异步复位信号。若74LS160从0000状态开始计数,则第六个时钟脉冲上升沿到达时进入0110状态,使RS锁存器置位,

端输出的低电平作为74LS160的异步复位信号。若74LS160从0000状态开始计数,则第六个时钟脉冲上升沿到达时进入0110状态,使RS锁存器置位,![]() 端输出低电平。74LS160在0110状态作短暂停留后,迅速转入其它状态,如0010或0100,译码器输出的负脉冲消失。如果我们把这个窄脉冲直接作为74LS160的异步复位信号,计数器不一定能够可靠地工作。如果我们把这个窄脉冲作为RS锁存器的置位信号,把时钟脉冲作为RS锁存器的复位信号,再将RS锁存器的

端输出低电平。74LS160在0110状态作短暂停留后,迅速转入其它状态,如0010或0100,译码器输出的负脉冲消失。如果我们把这个窄脉冲直接作为74LS160的异步复位信号,计数器不一定能够可靠地工作。如果我们把这个窄脉冲作为RS锁存器的置位信号,把时钟脉冲作为RS锁存器的复位信号,再将RS锁存器的![]() 作为74LS160的异步复位信号,计数器一定能够可靠地工作,因为

作为74LS160的异步复位信号,计数器一定能够可靠地工作,因为![]() 输出的负脉冲的宽度与时钟脉冲高电平的持续时间相等。

输出的负脉冲的宽度与时钟脉冲高电平的持续时间相等。

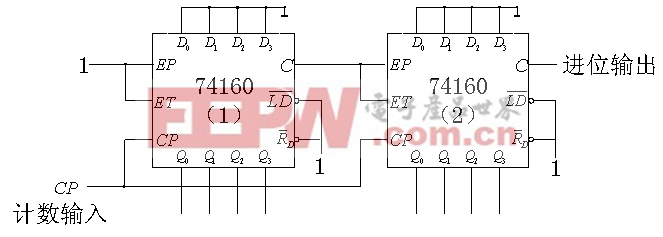

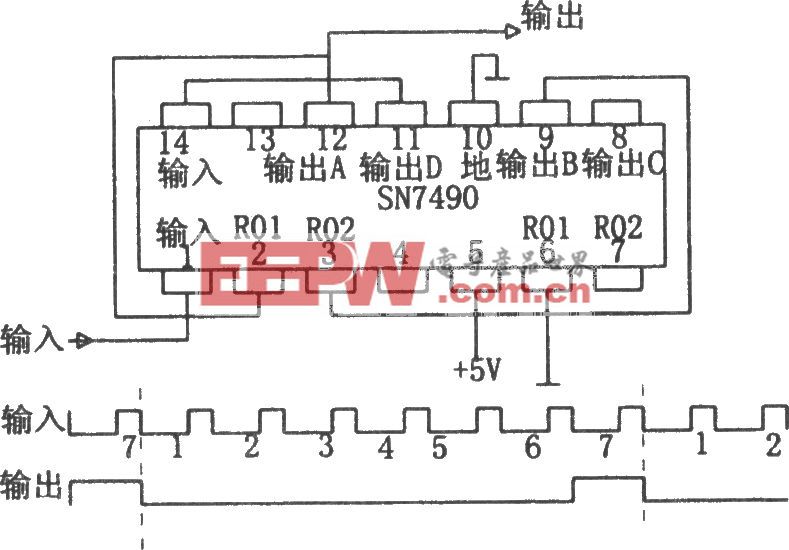

第二个例子要求我们构成一百进制计数器,也就是说,计数器的状态为0010到9910。因为100等于10乘以10,所以我们可以用两个74LS160构成一个一百进制计数器,其中一个计数器的状态表示个位数,另一个计数器的状态表示十位数,后者在前者的进位信号控制下计数。我们有两种方案。第一种方案称为并行进位方式[图5.3.39]。

图5.3.39 例5.3.3电路的并行进位方式

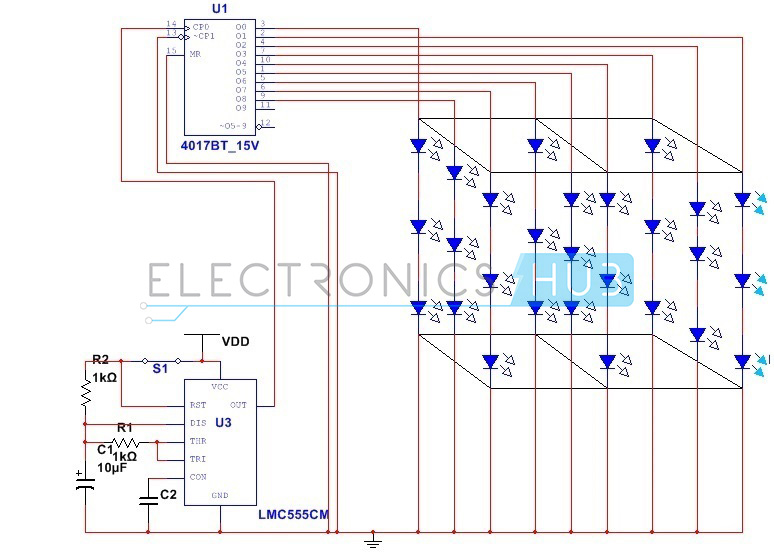

这种方案的特点是两个74LS160的CP端都接到时钟脉冲上。不过,第一个74LS160始终工作在计数方式,每一个时钟脉冲都使其状态发生变化;第一个74LS160只有在第一个74LS160进位输出为高电平是才工作在计数方式,每十个时钟脉冲才使其状态发生变化。若计数器从0010状态开始计数,则第九个时钟脉冲到达后,第一个74LS160的状态变为910且进位输出变为高电平,使第二个74LS160进入计数方式。因为第二个74LS160进入计数方式的时间比第九个时钟脉冲到达的时间晚,就是说,第九个时钟脉冲到达时第二个74LS160尚未进入计数方式,所以,第九个时钟脉冲并不能使第二个74LS160的状态发生变化,其状态仍为010。于是,计数器的状态为0910。第十个时钟脉冲到达后,第一个74LS160的状态变为010且进位输出变为低电平,使第二个74LS160退出计数方式。因为第二个74LS160退出计数方式的时间比第十个时钟脉冲到达的时间晚,就是说,第十个时钟脉冲到达时第二个74LS160尚未退出计数方式,所以,第十个时钟脉冲使第二个74LS160的状态发生变化,其状态变为110。于是,计数器的状态为1010。第二种方案称为串行进位方式,这种方案的特点是,两个74LS160都始终工作在计数方式。不过,第一个74LS160的CP端接到时钟脉冲上,每一个时钟脉冲都使其状态发生变化;第一个74LS160的CP端接到第一个74LS160进位输出上,每十个时钟脉冲才使其状态发生变化。经常有学生问:“为什么在第一个74LS160的进位输出端和第二个74LS160的时钟脉冲输入端之间要加上一个非门呢?”这里面有点儿奥妙。若计数器从0010状态开始计数,则第九个时钟脉冲到达后,第一个74LS160的状态变为910且进位输出变为高电平。如果没有这个非门,第一个74LS160的进位输出端的电平变化将使第二个74LS160的状态发生变化,其状态变为110。于是计数器的状态就从0810变成1910,而不是我们所希望的0910。有了这个非门,情况就不一样了,因为第一个74LS160的进位输出端的脉冲上升沿被非门转换成下降沿,所以第一个74LS160的进位输出端的电平变化并不能使第二个74LS160的状态发生变化,其状态仍为010。于是计数器的状态就从0810变成我们所希望的0910。第十个时钟脉冲到达后,第一个74LS160的状态变为010且进位输出变为低电平。因为第一个74LS160的进位输出端的脉冲下降沿被非门转换成上升沿,所以第一个74LS160的进位输出端的电平变化使第二个74LS160的状态发生变化,其状态变为110。于是计数器的状态又从0910变成1010。

我们再举一个用74LS160构成二十九进制计数器的例子。因为29是一个素数,除了1和它本身外,不能表达为两个整数的乘积,所以我们要把工作分解成两个步骤。第一步,我们用两个十进制计数器构成一个一百进制计数器;第二步,我们用这个一百进制计数器构成二十九进制计数器。第一步可以采用并行进位方式或串行进位方式实现;第二步可以用置位法或复位法实现。因为这里要对两个74LS160同时置位或复位,所以也称为整体置位法或整体复位法。

评论