0.6 V CMOS轨至轨运算放大器

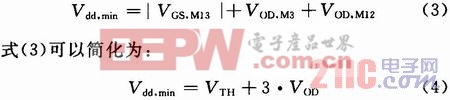

本文设计的低压运算放大器的核心电路如图3所示,该电路由电平偏移互补差分对(R1,R2,M1~M4)和对称运算放大器(M5,M6,M13~M16)组成。图3中,电平偏移电流产生电路(Level-shift Current Generator)与文献中相同,其中Ish供给M7~M10。但在文献中,采用了共源共栅结构,其在超低电源电压下工作是不适合的。从图3可以看出,该电路能够工作的最小电源电压是:

本设计中,对于0.6 V的电源电压,在0.13μm CMOS工艺制程下,阈值电压约为0.4 V,过驱动电压设计为0.06 V。

2 模拟结果与讨论

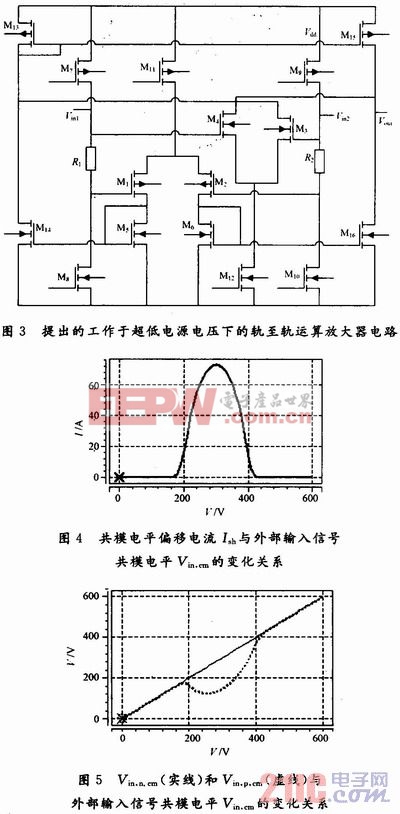

图4为共模电平偏移电流Ish与外部输入信号共模电平Vin,cm的变化关系。本文引用地址:http://www.eepw.com.cn/article/187568.htm

图5为内部NMOS差分对输入端的共模电平Vin,n,cm和PMOS差分对输入端的共模电平Vin,p,cm与外部输入信号共模电平Vin,cm的变化关系。可以看出,当外部输入信号共模电平处于中间区域时,Vin,p,cm会降低,此时PMOS输入差分对会导通。因此该共模电平偏移输入级实现了在低和中Vin,cm时PMOS输入差分对导通,高Vin,cm时NMOS输入差分对导通,即实现了轨至轨输入。

评论