基于LPC2132数字信号源的设计与实现

1.2 AD9850电路设计

信号产生采用单片机LPC2132和专用DDS芯片AD9850组成,电路原理如图3所示,单片机与AD9850的数据传送采用并行接入方式,电路通过J1接口与LPC2132相连,其中,D0~D7与单片机系统的数据总线相连,RESET、FQ_UD、W_CLK分别与单片机的I/O口线相连。AD9850内部DAC为电流输出,其满量程输出电流可通过外接电阻R1调节,IOUT和IONTB为DAC输出的电流信号。通过外接电阻R3和R4将电流信号转换为电压信号。由DAC输出的电压信号经过低通滤波,目的在于滤除高频杂散和谐波,设计中采用了一片集成集成开关电容低通滤波器LT6600,截止频率为10MHz,内部带有全差分放大器,通过改变R7和R8的阻值可获得不同的放大倍数。AD9850内部设有高速电压比较器,将低通滤波器的输出信号和一固定的直流电平(来自LT6600的第2脚和第7脚)送到比较器的输入端,可得两路与正弦信号频率相同且互为反相的方波信号。本文引用地址:http://www.eepw.com.cn/article/185507.htm

主要技术参数分析:1)具有极高的频率分辨率和相位分辨率,且相对频带很宽。这是DDS最主要的优点。因为DDS的频率分辨率决定于相位累加器的位数和参考时钟频率,只要相位累加器的位敷足够长,DDS的频率分辨率可以达到足够高,所以说频率分辨事和相位分辨率是传统的频率合成方法无法比拟的。2)杂散抑制差,也是DDS的主要缺点。DDS在寻址波形表时,都采用了相位截断技术,它的直接后果是给DDS输出引入了杂散。同时波形存储器中的波形幅度量化引起有效字长效应,还有DAC的非理想特性,都导致DDS的杂散抑制性能差。3)不能够获得很高的相位噪性能指标。DDS的相位噪声主要由参考时钟信号的性质、参考时钟的频率与输出频率之间的关系以及器件本身的噪声决定。在实际工程中,必须考虑包括相位累加器、ROM、和DAC等各部件噪声特性对DDS相位噪声性能的影响。

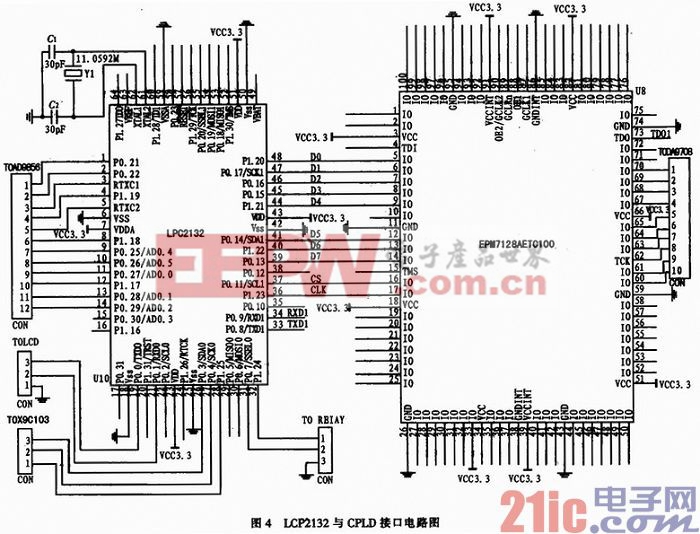

1.3 LPC2132+CPLD电路设计

由于DDS技术的实现依赖于高速、高性能数字器件,控制方式也比较固定,专用DDS芯片一般只能产生正弦波和方波。三角波的产生尽管可将方波信号经积分电路进行积分转换来实现,但很难稍足不同频段对积分电容的要求,因此用DDS芯片产生方波实现三角波信号的输出频率范围十分有限。

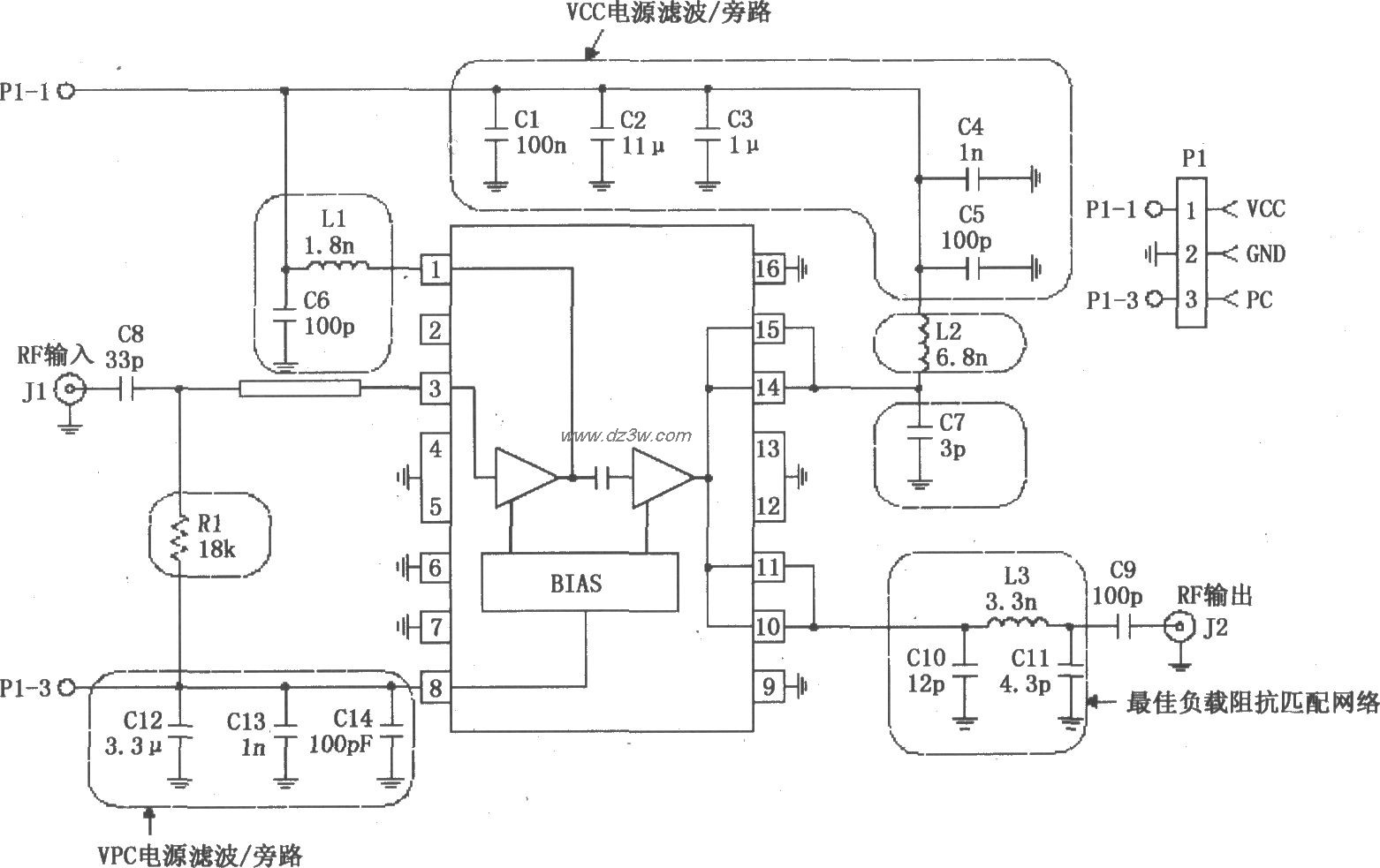

三角波信号发生电路的设计由两部分组成,第一部分是单片机和CPLD(EPM7128AETC100)接口电路设计,如图4所示,单片机LPC2132通过并行接口向CPLD中的频率字寄存器发送频率字,向CPLD中的双口RAM传送波形点阵数据。并行接口信号线包括:8位数据线,读信号、写信号、片选信号、地址锁存信号、地址信号。低8位地址线通过CPLD内部的锁存器产生,这样可以减少并行接口信号的数量。第二部分是用于三角波波形重建,由高速D/A转换器AD9708和单片集成滤波器LT6600组成如图5所示,AD9708由CPLD直接控制,AD9708的数据线和时钟线与的I/O脚相连,设计中将模拟电源输入端串接一磁珠再与数字电源连在一起抑制杂散噪声。为了获得相对纯净的波形信号,D/A转换器的输出的应加低通滤波器,以滤去镜像频率分量和谐波分量。低通滤波器的设计采用单片集成滤波器LT6600,输出带宽大于2MHz,通带增益为12 dB,LT6600采用单端输入、双端输出的形式,来自AD9708的模拟输入信号,送LT6600的V+输入端,通过J3口输出差分三角波信号。

评论