基于VCA822的可编程增益放大器

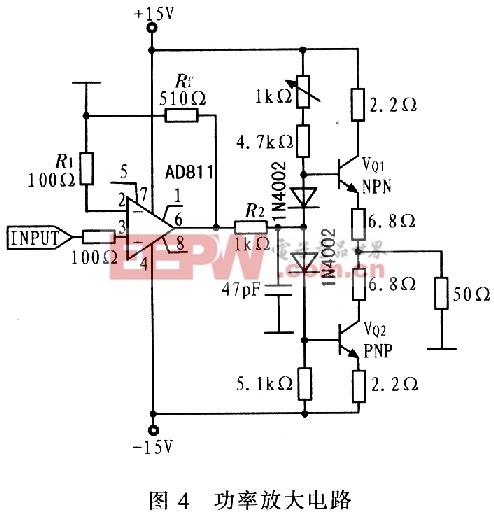

2.4 后级功率放大电路

为了增加系统负载能力,考虑到运算放大器AD811自身负载驱动能力的限制,这里选用AD8l1配合高频中小型功率对管2N3904(NPN型)和2N3906(PNP型)(两功率管特征频率fT=300 MHz)搭建0CL功率放大器。前级由AD811组成同相放大器,放大倍数为Av=1+Rf/R3;后级选用功率对管扩流构成甲乙类功率推挽输出形式提供负载驱动电流。经实验测试,输出端接50 Ω负载时,无失真的最大输出电压峰对峰值达到18 V。电路原理图如图4所示。本文引用地址:http://www.eepw.com.cn/article/173242.htm

2.5 数字检波

本设计中的峰值检波电路基于信号频谱搬移理论,由于A/D转换器在单一采样率进行采样时会出现盲区频段,故以2个特殊频率(双频)先后对信号进行采样,提取采样结果中的最大值即可得到周期信号峰值。这种方法可兼顾高低频,适合应用于该系统100 Hz~15 MHz的情况。采用A/D转换器MAXl97,利用2个采用率f=50.000 kHz,f2=50.005 kHz互补采样盲区,可得到良好采样效果。设置A/D采样率的方波信号由FPGA提供。

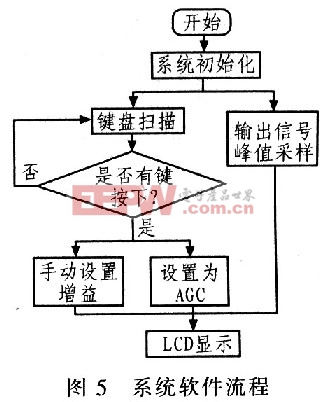

3 系统软件设计

该系统软件采用模块化和层次化的设计思想。采用模块化设计思想,要对某一子控制器控制,只需调用相应的控制模块即可。模块内采用层次化设计,把底层的硬件接口处理编制为独立底层子程序,并向上提供处理数据,且对上层功能模块屏蔽底层硬件接口部分;最后,主程序只需调用相关的功能模块就可方便构建系统。

本系统软件部分主要由单片机组成,其中主要包括系统初始化、中断的响应和中断的处理。该设计功能实现以键盘的按键中断为主线,通过读入用户输入的键值,在相应的中断响应函数中与FPGA中对应的控制模块以总线的方式进行及数据的交换,触发FPGA内相应的控制时序,实现对信号的放大和测量。系统软件流程如图5所示。

4 数据测试

该系统利用数字合成信号源、双踪示波器、仿真机、交流电压表进行测试。调节输入信号的频率,并利用交流电压表记录输出电压的有效值。测试结果表明,放大器的放大倍数在10~58 dB内9级可调,-3 dB点为100 Hz~15 MHz,且放大效果稳定。对于放大器的AGC功能,将输入信号频率固定,改变电压大小,输入信号峰值为9 mV~1 V时,可将输出信号稳定在峰值为4.5~5 V的电压范同内,故AGC动态范围大于40 dB。预置放大器放大倍数58 dB时,输入端接地,输出噪声电压小于10 mV。

5 结论

该系统设计是以VCA822为核心的可控增益宽带放大器。经测试,系统通频带为100 Hz~15 MHz,增益10~58 dB内9级可调,且放大器AGC功能的动态范围大于40 dB。此外,系统输入端采用MAX477接成同相放大电路,使得系统输入电阻达到MΩ数量级。后级AD811和分立元件搭建的功率放大电路,提高了系统带负载的能力。系统还采用多种抗干扰措施,有效保证放大器精度,并具有良好噪声和线性。

评论