单片机双向并行接口总线的长线传输技术

三、总线驱动能力问题及其解决方案

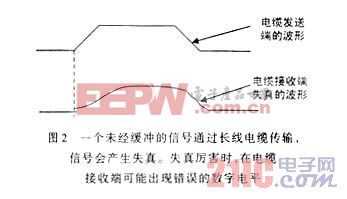

与一般单片机总线扩展技术中考虑的总线驱动能力问题不同,在用长线电缆实现总线接口连接时也会产生总线驱动能力问题。前者主要考虑的是总线的交、直流负载能力,从而确定总线上允许挂接的负载个数;后者产生的根本原因是长线电缆本身表现为高容性负载(分布电感的影响很小,一般不予考虑),在有限电流的驱动下,信号在电缆一端传送到另一端时,就会产生明显的信号衰减和畸变现象,如图2所示。所以用长线电缆实现总线驱动时主要考虑的是长线本身作为负载对总线驱动能力的要求。

工程实践中发现,晶体管-晶体管逻辑(TTL)电平的单端信号几乎很难在一个输入/输出(I/O)周期内驱动1 m以上(甚至更短)的电缆;而且我们还发现一个有意思的现象,尽管互补金属氧化物半导体(CMOS)逻辑电平的抗干扰噪声容限明显高于TTL电平,但相同电源电压(5 V)下的高速CMOS(HCMOS)接口器件(主要指缓冲器端)的长线驱动能力却明显地低于TTL接口器件。定性地理解这一现象可解释为,噪声容限大的器件往往产生的噪声也大,CMOS器件属于容性负载,每个引脚有大约10 pF的输入电容,输入阻抗极高,对长线电缆的阻抗不匹配导致的反射现象尤为严重,故抗干扰能力比TTL器件差许多。器件抗干扰能力通常与输入阻抗有关,输入阻抗越低,抗干扰能力越强。

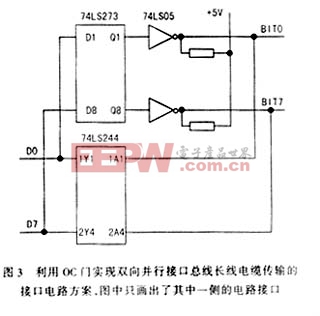

在通常的总线接口驱动器/缓冲器方案中,例如使用74245芯片作驱动器/缓冲器,要提高长线电缆连接时的总线驱动能力,解决办法主要有2种,一是适当降低传输速率,二是在总线两端加上拉电阻。前者是为了避开容性负载对脉冲前沿的平滑作用和反射波的干扰,这是一个暂态过程;后者是为了提高信号高电平,也起到降低输入阻抗、减小反射波干扰的作用。笔者曾经想利用这种方案在一个I/O周期内实现2 m长电缆的双向并口通信,但失败了。正如前面强调指出的那样,失败原因当然并不仅仅是总线驱动能力问题。成功的实践是使用OC门作驱动器。OC门具有很强的总线驱动能力,它允许输出端直接相连实现“线与”功能。设计难点在于如何把单向驱动改造为双向驱动,图3给出了具体电路方案。

其工作原理为:数据写出时由地址译码电路的片选信号选通74373锁存器,再由OC门7405驱动至远端缓冲器74244;数据读入时先向74373输出逻辑“0”,使已方OC门置于逻辑高状态,正确实现“线与”功能,再由地址译码选通74244读数。

图3的方案具有相当的设计启发性,稍加改造就可以适应许多要求高速、大容量双向通信的场合。比如在74LS244侧增加或干脆换成先进先出(FIFO)器件,就可以支持高速、大容量的成块数据交换。

四、电磁干扰及其解决方案

使用单端信号进行长线电缆传输时,有2种电磁干扰是不能忽视的:线间窜扰和地线噪声。线间窜扰是当2条或多条较长的的导线相平行而又靠得很近时,其中一条导线上的信号将对其它导线产生干扰。线间窜扰是一种近场(即距离干扰源小于的场,其中λ为电磁波长)耦合干扰,受扰线上的影响来源于传输线间的分布电容和分布电感引起的电磁耦合。线间窜扰大多发生在多芯电缆、束捆导线或印制板上的平行导线之间,窜扰强度与相邻两信号线间互阻抗和信号线本身的特性阻抗有关,并与线间距成反比,与线平行长度成正比。对线间窜扰的抑制,一般采用一些常规而有效的方法。当用扁平电缆作连接电缆时,在相邻信号线之间插入地线,可把导线间的耦合电容转化为对地电容;如果窜扰比较严重,还可以使用带双绞线结构的扁平电缆,这种电缆对抑制静电干扰和空间电磁干扰也有效果;也可以考虑采用多股双绞线结构的屏蔽电缆。

地线造成电磁干扰的主要原因是地线存在阻抗,当电流流过地线时,会在地线上产生电压,这就是地线噪声。在这个电压的驱动下,会产生地线环路电流,形成地环路干扰。当2个电路共用一段地线时,会形成公共阻抗耦合。增加地线的直径对于减小直流电阻是十分有效的,但对于减小交流阻抗的作用很有限;减小交流阻抗,一个有效的办法是多根地线并联。当2根导线并联时,其总电感:

ИL=(L1+M)/2 (7)И

式中L1是单根导线的电感;

M是两根导线之间的互感。

正是因为地线的交流阻抗特性,使得地线成了电路中事实上的最大噪声源。单端信号的传输长度最终受限于地线长度。抑制地线噪声的最理想的办法是对电缆两侧的电路进行电气隔离。参考文献[2]给出了一种利用高速光耦6N137对MCS-51系列单片机的系统总线进行双向高速隔离的很新颖的方案。但笔者认为这种隔离方案对以双向并行通信为目的应用来说,已基本失去实用价值。因为光耦是单向传输器件,最终隔离的结果将是全双工信道,而并行全双工信道的长线传输方案因技术、器件、线路成本上升很多而在工程上很少应用。所以,对TTL电平的单端信号的双向传输来说,必须严格限制电缆长度,一般不能超过5 m。

五、 结束语

双机并行通信技术普遍应用于短距、高速、大容量通信场合,但其高速性能受通信距离的影响很大,以更多的技术来实现并行通信长线传输的可靠性和高效性在经济上是得不偿失的。本文针对单片机系统之间的双向并行总线的长线传输问题进行了一些分析和讨论,并给出了几种廉价的解决方案。一般说来,对2 m长的并行通信电缆,数据传输率是完全可以达到500 kbit/s~1 Mbit/s。遵循器件解决的原则,也可以考虑采用并行接口标准器件,如IEEE-1284并行接口标准,这些标准接口器件已集成了端接元件并对连接器、电缆有严格的电气要求。但即使这样,在2 m长的电缆上也很难达到2 Mbit/s的数据传输率。

参考文献

[1]邵时,张汝杰.高速计算机系统中信号可靠传输技术[J].微型机与应用,1998,(12).

[2]刘大健,陈降道.单片机系统总线级的光电隔离[J].微型机与应用,

1998,(6).

[3]张松春,竺子芳,赵秀芬,蒋春宝.电子控制设备抗干扰技术及其应用(第2版)[M].北京:机械工业出版社,1995.

[4]王幸之,王雷,翟成等.单片机应用系统抗干扰技术[M].北京:北京航空航天大学出版社,1999

评论