8051单片机的I2C接口并行扩展

1 引 言

本文引用地址:http://www.eepw.com.cn/article/171690.htmI2C总线接口器件在视频处理、移动通信等领域的应用已经非常普遍。另外,通用的I2C总线接口器件,如带I2C总线的RAM,ROM,A/D,D/A,LCD驱动器等,也越来越多地应用于计算机及自动控制系统中。随着I2C接口器件越来越广泛的应用,8051系列单片机与他之间的通信越来越频繁。

8051系列单片机与I2C总线接口器件通信时,8051的通用口与I2C总线器件的SCL,SDA连接。根据I2C 总线数据传输协议,8051必须对其两个通用口进行频繁的置位、清零。根据基于51指令系统编制的汇编程序,传送一位数据,需要9个机器周期,而对于 8051,一个机器周期要耗费6个时钟周期,即用54个时钟周期才能传送一位数据。如此则极大地占用了CPU的工作时间,降低了系统的工作效率,导致I2C器件的优势难以显现。因此,有必要设计8051与I2C总线的专用接口电路。该接口电路能够对I2C总线上的数据进行自动收发,而CPU只需要通过并口访问该接口电路中的有关寄存器就可以实现与I2C器件的数据交换,从而使整个系统的性能得到提高。本设计用VHDL硬件描述语言为工具,用ALTERA公司的 MAXPLUSⅡ软件进行编译仿真,下载芯片为EPM7128SLC84-15。

2 设计目标和要求

为了提高数据传送的速度,设计一个I2C接口电路。8051不直接与I2C器件交换数据,而是通过并口与该I2C接口电路交换数据,I2C总线上的数据传送也通过该I2C接口电路来完成。从而通过CPU的外部存储器读写指令就可实现与I2C器件的数据交换,使对串口的操作用并口的方式来实现。

在I2C接口电路内部有一个控制寄存器CI0和一个数据寄存器CI1,即I2C接口电路占用两个地址。通过写控制寄存器CI0的内容实现对I2C接口电路的编程,读写数据寄存器CI1的内容实现与I2C器件的数据交换。在CI0中的内容定义了8051对I2C器件进行操作的类型(读或写)和I2C器件内地址的字节数等信息,使I2C接口电路能够识别从8051传来的数据是地址还是数据、8051将要发送数据还是接收数据以及数据的长度等。

如果8051要发送数据给I2C器件,则根据I2C总线协议,在数据CI1接收到第一个数据后启动I2C总线,然后将CI1中的数据进行并串转换后逐位发出,发出完毕后设置一个标志位,使8051知道可以发送下一个总线后首先写I2C器件内地址,然后进行数据接收,进行串并转换后将接收到的数据装入CI1中,再设置标志位,使8051知道可以读出数据。

根据上述设计要求,I2C接口芯片的引脚如图1所示。其中clk可以使用独立的时钟,使I2C总线的位传送速度远高于8051的位操作,从而可使I2C总线的数据传送接近并口的数据速率;a0是地址信号输入,a0=0时进行CI0写操作,当a0=1时进行CI1读/写操作;bz为标志输出位,bz=0时,8051需要等待,bz=1时8051可以对CI1操作。

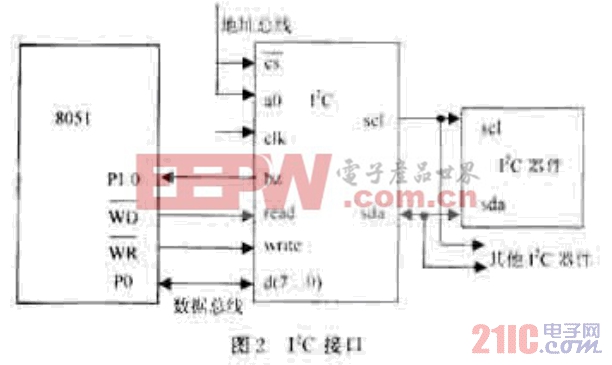

I2C接口芯片在系统中的情况如图2所示。这里8051对I2C接口芯片操作使用了查询方式,也可以改用中断方式。

3 并行接口设计的实现

3.1 接口设计的内部结构

该芯片的内部结构图如图3所示。系统由控制寄存器CI0,数据寄存器CI1,并串转换,串并转换,移位寄存器以及I2C控制模块6部分构成。

评论