51单片机(二):单片机内部定时/计数器和中断系统

表4 IE寄存器

EA:中断允许总控制位。EA=0,禁止所有中断;EA=1,开放所有中断,但是否允许各中断源的中断请求,还要取决于各中断源的中断允许控制位的状态。这点要注意,初学者往往容易忘了开放所有中断,从而导致没法进入中断源。

ET2 :时器/ 计数器T2 的中断允许位。

ES :串行口的中断允许位。

EX1 :外部中断1(INT1) 的中断允许位。

EX0 :外部中断0(INT0) 的中断允许位。

以上7 个中断允许控制位为0 时,禁止中断,为1 时允许中断。

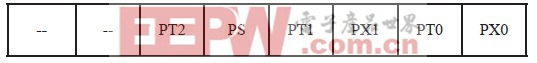

表5 IP寄存器

PT2 :定时器/ 计数器T1 中断优先级控制位。

PS :串行口中断优先级控制位。

PT1 :定时器/ 计数器T1 中断优先级控制位。

PX1 :外部中断1 优先级控制位。

PT0 :定时器/ 计数器T0 中断控制位。

PX0 :外部中断0 中断优先级控制位。

以上6 个中断优先级控制位分别为“0”时为低级中断,为“1”时为高级中断。如果几个同一优先级的中断源同时向CPU 申请中断,CPU 通过内部顺序查询逻辑电路,按自然优先级顺序确定该响应哪个中断请求。自然优先级由硬件形成,其优先级别从高到底为外部中断0、定时器/ 计数器T0、外部中断1、定时器/ 计数器T1、串行口中断、定时器/ 计数器T2。

至此,对定时器控制相关的重要寄存器都介绍完毕了,接下来通过编写程序来进行验证实践。

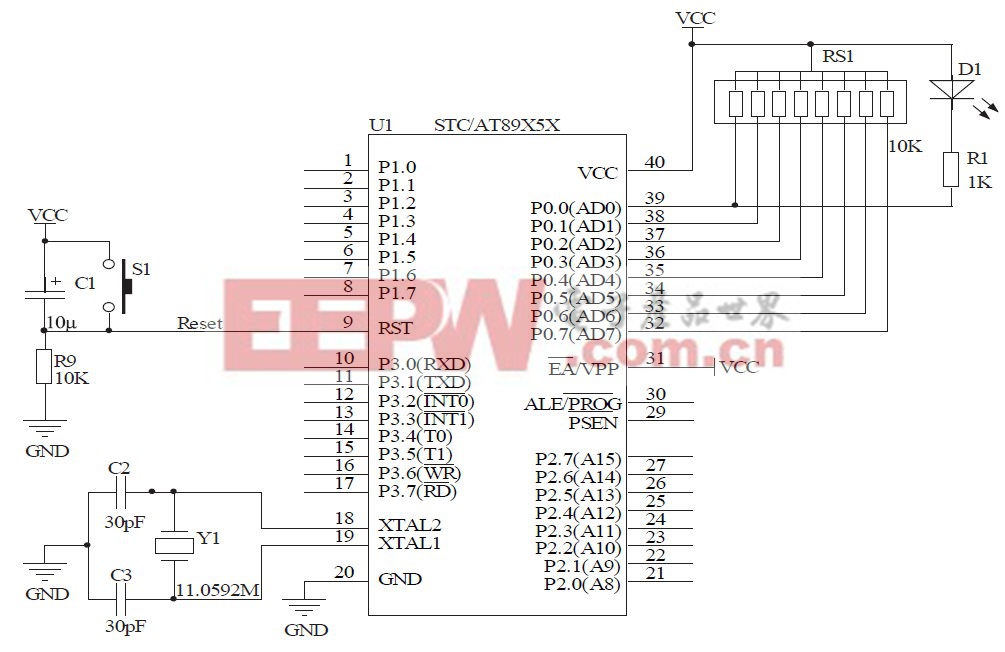

二、电路详解

此讲采用和上讲一样的电路,在此不做赘述(见图1)。

图1 定时器应用实验电路图

评论