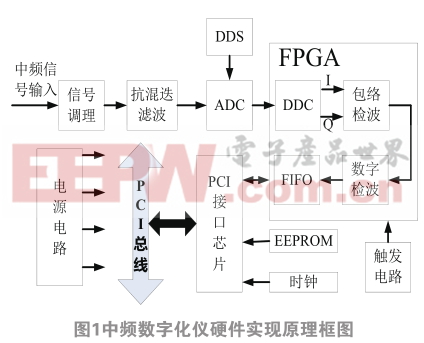

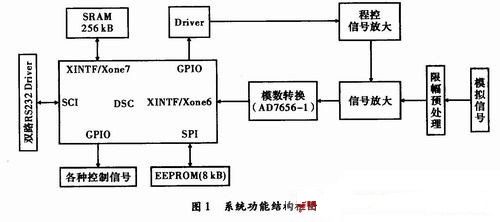

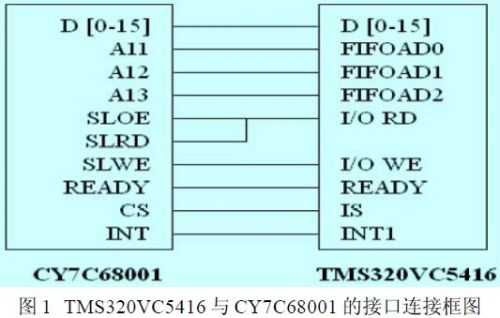

杨志兴,王瑞霞,高长全(电子测试技术重点实验室,山东 青岛 266555) 摘 要:针对PXI测试系统构建中需要的高速数据采集设备,提出一种基于PXI总线的中频数字化仪的设计方案。该设备可以实现400 Msps的实时采样率和14位的采样精度;软件开发模式采用上位机应用程序和底层动态库相结合的开发模式,方便不同用户的定制。驱动程序通过WDM开发,采用Block DMA实现数据的上传。经过联合调试,本系统稳定工作在Windows平台下,实现了数字化仪要求的各项功能。不仅满足当前项目的需求,还可应用于雷达

关键字:

202005 PXI 中频数字化仪 WDM Block DMA 中断

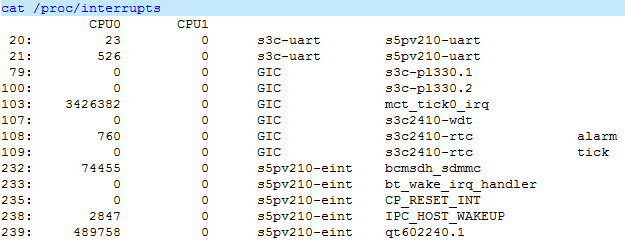

你永远也唤不醒一个装睡的人,但是你可以一巴掌呼醒他。可如果一个嵌入式系统休眠之后,就犹抱琵琶半遮面,千呼万唤醒不来了呢?笔者担纲开发的中控锁模块就醒不过来了。

关键字:

中断 嵌入式

四月的重庆已然百花盛开,春回大地,大自然又恢复了勃勃的生机,燕子挥舞着银光闪闪的翅膀,在湛蓝而悠远的天空中无拘无束地飞翔着,时而快速扇动着翅膀冲上天空,时而展开双翼低低滑翔。

关键字:

CAN 中断 堆栈

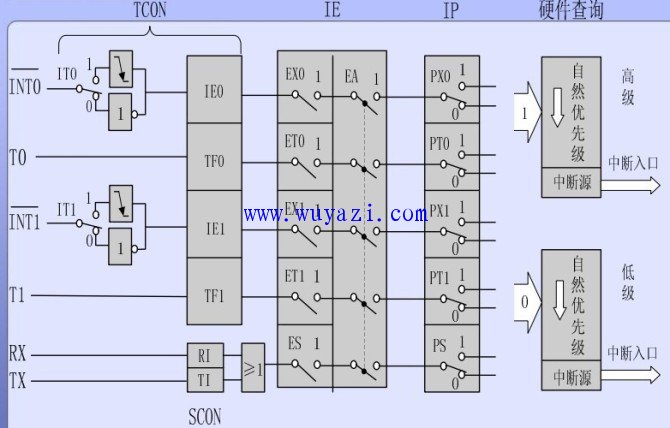

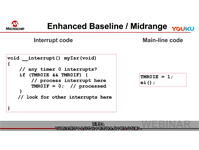

中断优先级的内容,大家先通过我的介绍大概了解一下即可,后边实际应用的时候我们再详细理解。 在讲中断产生背景的时候,我们仅仅讲了看电视和烧水的例子,但是实际生活当中还有更复杂的,比如我正在看电视,这个时候来电话了,我要进入接电话的“中断”程序当中去,就在接电话的同时,听到了水开的声音,水开的“中断”也发生了,我们就必须要放下手上的电话,先把煤气关掉,然后再回来听电话,最后听完了电话再看电视,这里就产生了一个优先级的问题。 还有一种情况,我们在看电视的时候,这个时候听到水开的声音,水开的“中断”发生了

关键字:

单片机 中断

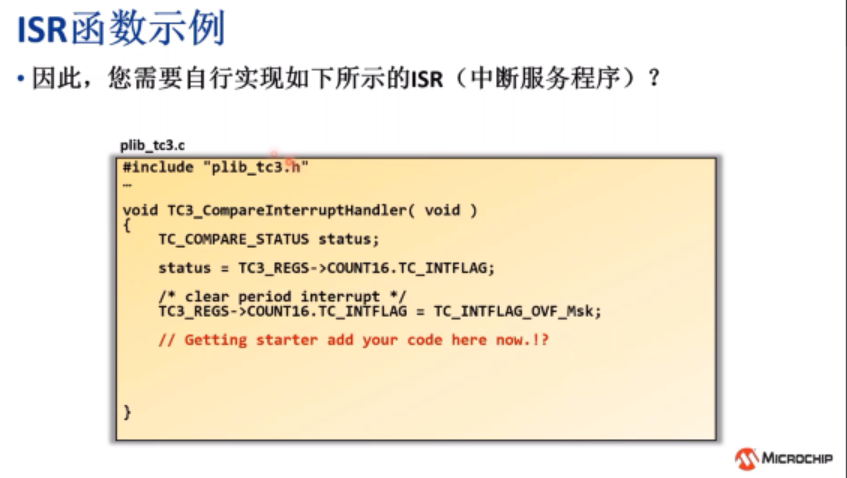

数字信号控制器(Digital Signal Controller, DSC)是将DSP内核与MCU接口相结合的微处理芯片。DSC同时具有数字信号处理能力和MCU控制接口,并且中断系

关键字:

DSC CPU 微处理芯片 中断 优先级级别

内部中断:一般是由硬件错误或者运算过程中出错引起的,一般是不可避免的; 外部中断:是处理器的外设发出的中断请求,如定时器中断,UART接收中断,外部中断一般都可以通过中断控制器进行屏蔽; 1.ITC功能概述: ……所有IO引脚都具有外部中断能力,每个端口都有独立的中断向量以及独立的标志;外设中断能力; ……软件中断能力(TRAP) ……具有灵活的优先级和中断等级管理,支持可嵌套和同级中断管理: ——多达4个软件可编程的嵌套等级;——最多有32个中断向量,其入口地址由硬件固定;——2个不可避免

关键字:

STM8 中断

在前几篇文章,GPIO的使用:点亮LED!中只讲述了IO口的输出,并没有输入,因为IO作为输入我建议采用中断方式,可以大大减轻CPU的运行时间。最常用的就是按钮的功能了,当然还有和其他芯片通信的功能。 前篇文章讲过GPIO可以通过寄存器设置为中断输入。 配置模式DDRCR1CR2配置模式上拉电阻 输入000悬浮输入 OFF 010上拉输入ON 001中断悬浮输入 OFF 011中断上拉输入ON 输出100开漏输出 OFF 110推挽输出 1x1输出(最快

关键字:

stm8s 中断

随着嵌入式微处理器性能的提高,集成的外围接口设备越来越多,而外围设备与处理器之间多采用中断方式进行通信,即使在没有操作系统的情况下,也常需要对多个外围设备的中断处理例程进行动态加载.

关键字:

中断 实时性 人机交互

为了管理中断请求的优先级并处理其他异常,Cortex-M0处理器内置了嵌套中断控制器(NVIC)。NVIC的一些可编程控制器控制着中断管理功能,这些寄存器被映射到系统地址空间里,它们所处的区域被称为系统控制空间(SCS)。

NVIC有以下特性: 灵活的中断管理; 支持嵌套中断; 向量化的异常入口 中断屏蔽 灵活的中断管理 Cortex-M0处理器中,每一个外部中断都可以被使能或者禁止,并且可以被设置为挂起状态或者清除状态。处理器的中断可以是信号

关键字:

Cortex-M0 中断

异常会引起程序控制的变化。在异常发生时,处理器停止当前的任务,转而执行异常处理程序,异常处理完成后,会继续执行刚才的任务。异常分为很多种,中断是其中之一。Cortex-M0处理器最多支持32个外部中断(IRQ)和一个不可屏蔽中断(NMI),中断事件的处理叫做中断服务程序(ISR),中断一般由片上的IO口的外部输入产生(边沿触发和电平触发)。 Cortex-M0处理器上可用的中断数量不确定,由厂商决定,最多32个外部中断。如果系统的外设很多,由于中断数目有限,多个中断源可能使用同一个中断连接。 除了

关键字:

Cortex-M0 中断

这个中断系列文章主要针对移动设备中的Linux进行讨论,文中的例子基本都是基于ARM这一体系架构,其他架构的原理其实也差不多,区别只是其中的硬件抽象层。内核版本基于3.3。虽然内核的版本不断地提升,不过自从上一次变更到当前的通用中断子系统后,大的框架性的东西并没有太大的改变。 1. 设备、中断控制器和CPU 一个完整的设备中,与中断相关的硬件可以划分为3类,它们分别是:设备、中断控制器和CPU本身,下图展示了一个smp系统中的中断硬件的组成结构: 图 1.1&nb

关键字:

Linux 中断

Tasklet作为一种新机制,显然可以承担更多的优点。正好这时候SMP越来越火了,因此又在tasklet中加入了SMP机制,保证同种中断只能在一个cpu上执行。在软中断时代,显然没有这种考虑。因此同一种中断可以在两个cpu上同时执行,很可能造成冲突。 Linux中断下半部处理有三种方式:软中断、tasklet、工作队列。 曾经有人问我为什么要分这几种,该怎么用。当时用书上的东西蒙混了过去,但是自己明白自己实际上是不懂的。最近有时间了,于是试着整理一下linux的中断处理机制,目的是起码从原理上能够

关键字:

linux 中断

“小王,醒醒,开始上课了,今天咱们开始讲中断,这可是高级东西,错过不补哈”我使劲推着睡梦中的小王。 “嗯?感情好啊,快点,快点”小王一听有新东西讲,像打了鸡血似的兴奋,连我都怀疑起她是不是性格中喜新厌旧。 不管那么多了,我讲我的,她厌她的… 啥叫中断?就是指cpu在执行过程中,出现了某些突发事件时CPU必须暂停执行当前的程序,转去处理突发事件,处理完毕后CPU有返回原程序被中断的位置并继续执行。 中断的分法不懂,分类就不同,向什么内外部中断,可/不可屏蔽中断…等等乱七八糟一大堆,我这里要说明的

关键字:

Linux 中断

在我的一个中断处理例程中有一下一段: save_flags(flags); cli(); set_gpio_mode_user(k->gpio_port, GPIO_MODE_IN); up = read_gpio_bit(k->gpio_port); set_external_irq(k->irq_no, EXT_BOTH_EDGES, GPIO_PULLUP_DIS); restore_flags(flags); 我

关键字:

S3C2410 中断

实时计算经常要求中断针对事件快速做出响应。只要掌握Zynq SoC中断结构的工作原理,就不难设计出中断驱动型系统。在嵌入式处理中,中断表示暂时停止处理器的当前活动。处理器会保存当前的状态并执行中断服务例程,以

关键字:

Zynq 中断

中断介绍

1.中断 zhōngduàn

半中间发生阻隔、停顿或故障而断开

交通中断

2.是指在计算机执行期间,系统内发生任何非寻常的或非预期的急需处理事件,使得CPU暂时中断当前正在执行的程序而转去执行相应的时间处理程序。待处理完毕后又返回原来被中断处继续执行或调度新的进程执行的过程。

中断是单片机实时地处理内部或外部事件的一种内部机制。当某种内部或外部事件发生时,单片机的中断系统 [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473