TMS320DM642的视频实时处理和显示系统的设计

3.2 GPIO接收模块

DM642共有16个GPIO引脚,引脚的输入/输出方向(输入/输出/高阻)可以通过编程设置。GPIO接口部分输入/输出引脚与其他接口引脚复用,可通过设置相关寄存器的值确定各GPIO引脚的工作方式。本设计采用DSP 16个GPIO引脚中的11个接收外部SPI接口传来的TS流数据。

SPI接口是MPEG-2视频码流传输接口标准之一,共11位并行信号,处理简单且扩展性强,目前一般的MPEG-2视频编码器的输出和视频解码器的输入都是标准的SPI接口信号。并行传输系统SPI包括1位时钟信号、8位数据信号、1位帧同步信号和1位数据有效信号。帧同步信号对应TS包的同步字节为047H,数据有效信号用来区分TS包的长度为188个字节或204个字节。当TS包长188字节时,数据有效信号一直为高电平,同时所有信号都与时钟信号保持同步。

3.3 外部存储器模块

外部存储器包括2片128 Mb的SDRAM和一片4 MB的Flash芯片,这3片存储芯片都连接在DM642的64位外部存储接口(EMIF)上。

SDRAM选用的是Micron公司的MT48LC4M3282,这种内存颗粒的架构为1M×32位×4,即每片芯片有4个bank,每bank行地址数为12(A0~A11),列地址数为8(A0~A7)。2片32位的SDRAM扩展成64位,且映射在EMIF的CE0空间。SDRAM的时钟由EMIF接口的AECLOUT1引脚提供,本设计中CPU主频采用600MHz,AECLOUT1输出配置为4分频的DSP主频时钟,即150MHz。

DM642片内无集成Flash或EEPROM,系统掉电后其内部存储器和外部SDRAM中的程序和数据将会全部丢失,因此DM642外部需要扩展Flash存储器,用来存储程序和重要的数据。本设计中Flash芯片选用的是AMD公司的32 Mb(4M×8位)异步存储器AM29LV033C。由于DM642的EMIF接口支持异步存储器,因此可直接与Flash相连。AM29LV033C内部的存储空间是分页的,共划分为64个大小为64 KB的扇区,通过地址线选择不同的扇区。AM29LV033C芯片有A[0:21]共22条地址线,但是DM642总共只有20条地址线(AEA[3:22]),由于二者地址线数量不同,DM642不能遍历Flash的所有地址单元。为了解决这个问题,在系统中采用CPLD对Flash进行页选控制。CPLD利用从DM642输入的空间片选信号ACE1、高位地址信号EA22、读写控制信号和输出使能控制信号,经逻辑运算输出页选控制信号FLASH_EXT[19:21],FLASH_EXT[19:21]接Flash的最高3位地址线,此3路信号把Flash存储器划分为8个页,每页存储器包含8个扇区。

3.4 I2C总线接口

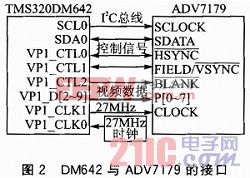

DM642集成有I2C总线接口,用于与I2C总线外设通信。本设计中DM642就是通过I2C总线模块对ADV7179进行配置的。TMS320DM642的I2C总线接口包括13个寄存器,分别为I2C总线时钟分频寄存器I2CCLKH及I2CCLKL、数据计数寄存器I2CCNT、数据接收寄存器I2CDRR、数据发送寄存器I2CDXR、中断使能寄存器I2CIER、中断源寄存器I2CISR、模式寄存器I2CMDR、主地址寄存器I2COAR、设备ID寄存器I2CPID、预分频寄存器I2CPSC、从地址寄存器I2CSAR和状态寄存器I2CSTR。通过对这些寄存器进行相应的读写操作即可完成和ADV7179的通信。DM642和ADV7179的接口如图2所示。由DM642产生与I2C总线外设通信所需的时钟信号。本文引用地址:http://www.eepw.com.cn/article/165680.htm

3.5 视频显示模块

TMS320DM642处理器集成了3个功能丰富的视频口VP0~VP2,每个视频口包括20位数据信号VPxD[19:0],2路时钟信号VPxCLK[1:0]以及3路控制信号VPxCTL[2:0]。时钟信号VPxCLK[1:0]作为视频口和外部编码、解码电路的同步时钟,控制信号VPxCTL[2:0]用于视频同步(如行同步、帧同步、场同步)和视频口使能控制。每个视频口划分为A、B两个通道,每个通道既可以配置为视频输入口,也可以配置为视频输出口,但是A、B两个通道在使用过程中必须没置为相同类型的输入或输出,不能一个通道配置为视频输入,另一个通道配置为视频输出。本设计中仅用到了视频口的输出功能,视频编码芯片ADV7179与DM642的视频口1相连接,具体信号线连接方式如图2所示。

评论