基于FPGA和CMX589A的GMSK调制器设计与实现

3.1 单片机软件设计

控制模块主要包括扩展矩阵键盘、LCD液晶显示、调制器参数控制。

单片机控制器的系统工作过程如下:

单片机初始化,LCD显示开始菜单,包括“高斯滤波器参数设置”和“FM调制器参数设置”两个选项;

进入“高斯滤波器参数设置”子菜单,包括“系统带宽设置”和“基带码元速率设置”,分别可以设置2种不同的滤波器带宽和8种基带码元速率,单片机根据系统设置在P2端口输出控制信息;

进入“调制器参数设置”的子菜单以设置“调制载波的中心频率”,可以设定四种不同的载波中心频率,并通过单片机P3口控制FPGA的调制载波的中心频率。

3.2 调制器的系统实现

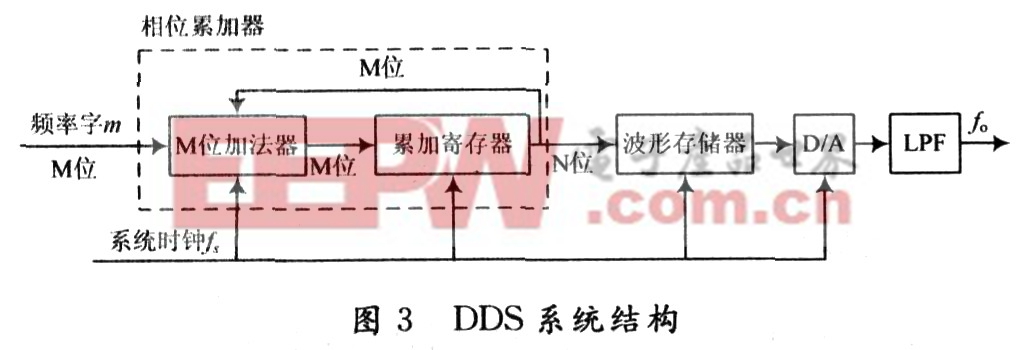

FM调制器采用DDS思想在FPGA平台上实现。DDS(Direct Digital Frequency Synthesizer,直接数字频率合成)是一种新型的频率合成技术,具有较高的频率分辨率,可以实现快速的频率切换。DDS系统主要由系统时钟源、相位累加器、正弦波查找表、D/A转换器和低通补偿滤波器组成,系统结构如图3所示。其中相位累加器是DDS系统的核心,它由N位加法器和N位相位寄存器组成。每来一位参考时钟脉冲,N位加法器将频率控制字和累积器的相位输出相加,把相加的结果送到相位寄存器的输入端。相位寄存器一方面将输出的相位数据反馈到加法器的输入端,以使加法器继续在时钟脉冲的作用下继续与频率控制字相加,另一方面又将输出的相位数据又作为波形存储表的地址输入。波形存储表把输入的地址相位信息映射成波形数据,最后经过DAC和低通滤波器得到模拟信号。

本设计采用20 MHz外部晶振作为时钟源,系统采用40位相位累加器,故频率字也取40位,所以系统的频率分辨率如下式所示:

FM调制器完成幅度到频率的转换是系统设计的关键。例如设定基带信号的速率为8 kHz,载波的中心频率为200 kHz(fword=“10995116277”),为了实现调制指数为0.5的FM调制器,FM调制器的频率差为4 kHz。FPGA根据8位A/D转换器输入的信号幅度值选择相应的频率字,从而控制输出信号的频率完成调频功能。载波的中心频率对应的A/D转换器中心幅值a in=“10000 0000”;当A/D转换器输入为O V(即a in=“0000 0000”)时,对应的调制信号的输出频率为198 kHz(fword=“10885165114”);当A/D转换器的输入为满刻度2 V(ain=“1111 1111”)时,调制输出频率为202 kHz(fword=“11105067440”)。把频率从198 kHz到202 kHz等分成255份,把相应的频率转换成40位频率字,则A/D转换器的256个幅值与256个频率字一一对应。在每一个系统时钟周期,频率控制字与40位的相位累加器的值相加结果存入相位累加器。由于选用的ROM查找表的地址线为10位,所以取相位累加器的高10位作为正弦查找表的地址。正弦查找表利用Cyclone内部的ROM模块完成查找表的设计,字长为10位,与所选用的DAC的数据位数相匹配。

评论