DS/FH混合扩频接收机解扩及同步技术的FPGA实现

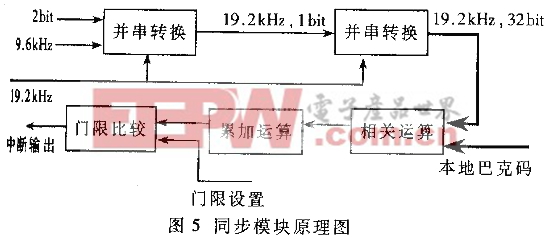

同步模块由位同步及帧同步电路构成,主要实现对信息数据的检测和提取,并识别一帧信息数据的帧头位置,实现跳频图案的同步。跳频图案的同步采用等待搜索同步法,开始时接收端频率合成器停留在某一单频点fi′,等待发射机的频率fi,当发射机的频率跳变为fi时,接收端本地的频率fi′与发送的频率fi混频后,输出中频fIF。DSP完成解扩解调运算后,得到的串行数据流送入位同步和帧同步电路,从数据流中提取出特征字,就可以获得一帧完整的数据,从而确定帧头的位置,即频率转换时刻,由此控制接收端频率合成器与发送端频率合成器同步跳变,实现跳频图案的同步。由于采用编码扩频调制方式,发送端每两位信息比特在一个PN码周期被编码为4种PN码中的一种。所以接收端在每一个PN码周期,对4组数据相关累加器的累加结果进行最大值比较,然后译码成相应的信息数据。信息数据送到同步电路,进行巴克码匹配相关,提取有效的信息位,并控制跳频时序完成跳频同步。同步模块原理如图5所示。

在每一个PN码周期,4组数据解调相关累加器解调出2bit信息数据。2bit信息数据以9.6kHz的速率送到同步电路。同步电路首先将信息数据进行并串转换,由9.6kHz、2bit的数据流变换为19.2kHz、1bit的数据流,变换后的数据流再经过串并变换,得到19.2kHz、32bit的并行数据流。根据信号格式,每一帧数据为32bit,相应的13位巴克码在一帧数据中的位置固定不变,所以提取每帧数据中相应位置上的13位数据比特与本地巴克码进行相关匹配运算,结果与门限值比较,如果符合门限设置,即有中断输出,通知外部设备读取相应数据。

3 实验结果

系统技术指标为:信息数据速率4.8kbps,比特率19.2kbps。跳频速率600hop/s,20个跳频点,跳频带宽68MHz,每跳32bit扩频码周期为256,码速率为4.9152MHz。

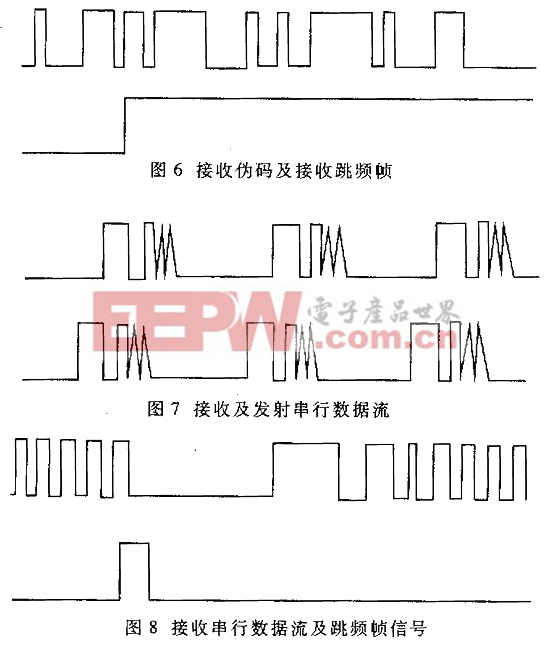

用TEKTRONIX 2221A数字存储示波器观测实验结果。图6~9为FPGA各测试点的测试结果。

图6中第一组波形是256码长本地接收同步伪码流,第二组为跳频帧同步信号,该信号对应的伪码相位即为解扩、跳频同

步时的相位。图7第一组波形为接收数据流,第二组波形为发射数据流,发射数据帧格式为00000000011111001101010000000000,帧同步码为13位巴克码1111100110101,8位信息数据为00000000。由图7可以看出接收端数据与发射端相同,但滞后于发射端,这是由于传输时延造成的。图8第一组波形为接收串行数据,第二组为跳频帧同步信号,该信号下降沿对应于一帧数据的起始,控制频率合成器进行频率转换。图9第一组波形为发射跳频帧信号,第二组为接收帧同步信号,接受帧信号上升沿与发射跳频帧信号的下降沿对齐,信号宽度大于发射端信号。这是因为控制频率合成器进行频率转换的updata信号需要一定宽度。

解扩及同步是DS/FH混合扩频接收机正确数据解调的关键,采用FPGA设计实现了多片专用芯片的功能,大大缩小了接收机体积,便于系统实现小型化、集成化。捕获及跳频同步等算法采用硬件实现,加快了捕获跟踪速度。FPGA的可编程性使电路的设计更具灵活性,并使系统具有“软”接收机的特点。实验结果表明FPGA系统设计是正确可行的。

评论