TMS320TCI6612/14 助力小型蜂窝基站实现高性能

TMS320TCI6612/14 助力小型蜂窝基站实现高性能

本文引用地址:http://www.eepw.com.cn/article/155721.htm产品公告

无线网络流量正日渐以数据为主。目前高速 3G 的全面铺开,以及速度更快的 4G 业务即将上线,无线数据速率随之水涨船高,因此,能否高效处理流经基站的大量数据已变得至关重要。只要采用合适的硅芯片技术和设计,基站就能够从容应对 4G 巨大的网络流量需求。营运商正转向异构网络,同时采用宏蜂窝及小型蜂窝解决方案来提供更出色的用户体验。多输入多输出 (MIMO) 天线阵列和高级接收器是新无线标准的关键元件,可提高网络带宽。将理想的处理元件用于小型蜂窝基站,可帮助开发人员按客户要求的速度提供所需的数据带宽。

TMS320TCI6612 与 TMS320TCI6614 均是最新无线基站片上系统 (SoC),可实现能够同时支持 3G 和 4G 双运行模式的业界最高性能小型蜂窝基站解决方案。TCI6612 和 TCI6614 是当前满足无线网络营运商对 4G 小型蜂窝基站以数据为中心性能的理想选择。多个 TMS320C66x DSP 核(其中 TCI6612 为两个,TCI6614 为四个)可提供可编程性能,而新型硬件加速器则可集中精力处理比特速率,帮助基站制造商实现较常规解码技术高出 40% 的频谱效率。此外,每个 SoC 中的完整 ARM RISC 内核还可进行控制处理,帮助开发人员为小型蜂窝基站设计低功耗的高性能解决方案。

TCI6612 与 TCI6614 SoC 建立在德州仪器 (TI) 可扩展 KeyStone 多核架构基础之上,可提供一系列处理元件,其中包括无线电加速器、网络与安全协处理器、支持定点与浮点功能的数字信号处理器 (DSP) 核以及 ARM RISC 处理器等,从而可为实现全面高性能的小型蜂窝基站提供理想的处理元件。基于队列数据包结构的 Multicore Navigator 与 TI Open Navigator 编程接口相结合,可帮助设计人员便捷地添加差异化增值特性。此外,TI 还在其 SoC 中集成了数字无线电,不仅可显著降低成本,而且还可简化小型蜂窝基站的集成与设计。

TCI6612 与 TCI6614 凭借每个 DSP 核的定点及浮点处理性能,可帮助基站设计人员充分发挥高速算法原型设计以及快速软件重新设计的优势,从而可降低成本、缩短开发时间。由于 C66x核具有如此强大的功能,因此只需极少量的内核就可实现比前几代 DSP 高出 4 倍的处理功能。随着内核数量的减少以及性能的提高,设计人员将享受简化的编程体验。

ARM RISC 核的集成可显著降低系统成本。与此同时,ARM Cortex-A8核能够帮助开发人员设计出低功耗高性能解决方案,不仅可在以数据为中心的应用上支持更多用户,而且还可为基站开发人员带来前所未有的高电源效率与高集成度。Cortex-A8 与整合数据包及安全处理器相结合,无需外部网络处理器。

主要特性

l 同步双模式无线基站片上系统 (SoC) 可为小型蜂窝基站实现无以伦比的高性能;

l 目前市场最高性能的多核小型蜂窝基站片上系统 (SoC),可为同步多标准无线基站实现无可匹敌的高吞吐量以及最低的时延;

l 位协处理器可提升 SoC 系统性能并支持高级接收器算法,与常规解码技术相比,可提高 40% 的频谱效率;

l TI 最新 C66x DSP 核将定点与浮点性能高度整合在同一芯片上,首次以定点速度支持浮点性能;

l 支持完整 ARM® Cortex-A8 处理器的 KeyStone SoC 可进行控制层处理;

l 协处理器的唯一解决方案支持各种标准,包括 WCDMA 芯片速率,无需 FPGA/ASIC;

l 网络协处理器与 Multicore Navigator 相结合,可为所有无线基站标准实现层2及传输加速;

l 基于 TI 最新 KeyStone 架构,不但支持从宏蜂窝到小型蜂窝的扩展与移植,而且还可降低产品开发的成本;

l Multicore Navigator 可为多核 SoC 带来单核简易性;

l 最佳功耗/性能比结合独特的节电休眠模式,可为基站实现最低功耗;

l 充分利用高性能 40 纳米工艺技术。

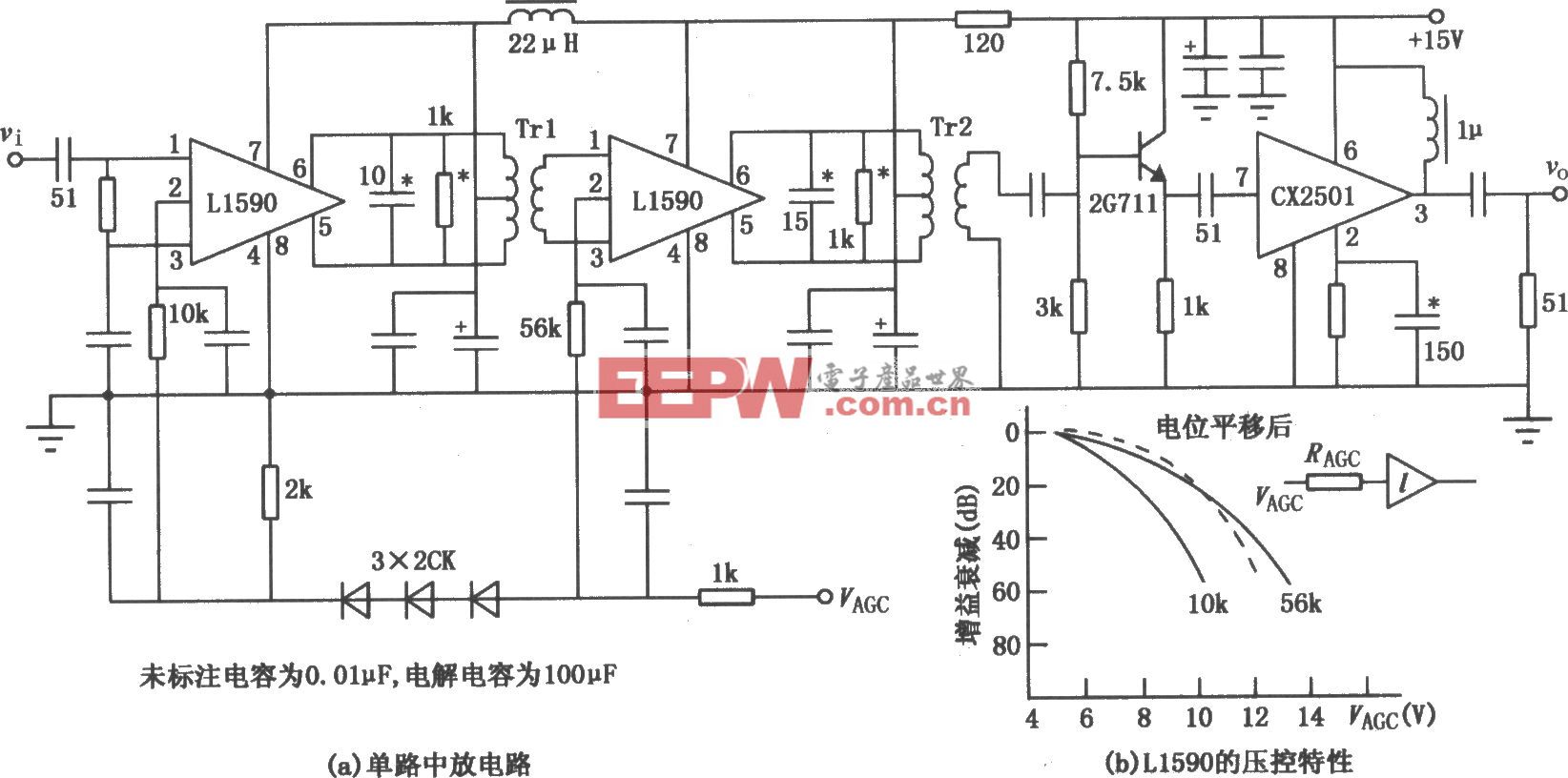

TCI6614 方框图

评论