基于DSP和SOPC数字信号发生器的设计

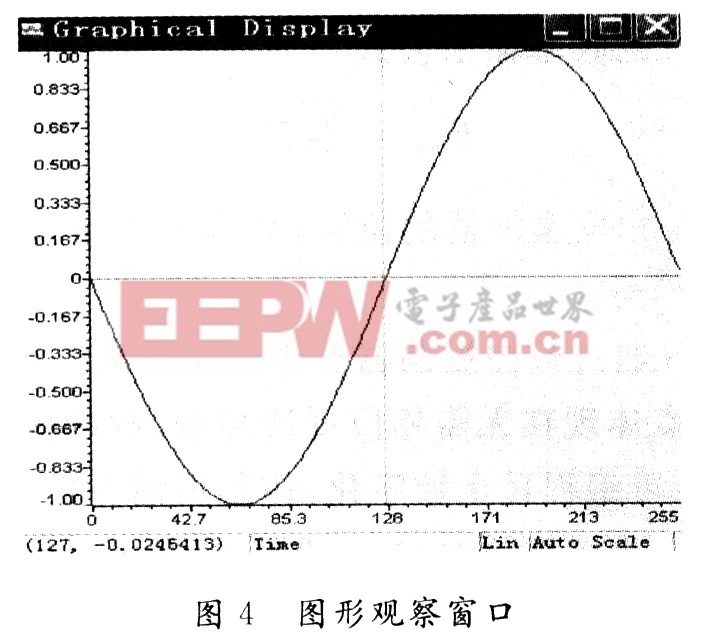

输出结果显示,在CCS图形观察窗口得到了频率稳定,信号干扰小,波形失真度较小的正弦信号;利用示波器也可观察到波形较好,稳定的正弦信号。

2 基于SOPC技术设计正弦信号发生器

尽管DSP处理器(如TI的TMS320系列)在过去很长一段时间几乎是DSP应用系统核心器件的惟一选择。但由于其自身的局限性,例如不灵活的硬件结构,使得其很难满足当今迅速发展的DSP应用市场。现代大容量、高速度、内嵌有各种DSP模块的FPGA和相应的SOPC技术出现,使得数字信号处理的实现更加容易。

2.1 DDFS原理

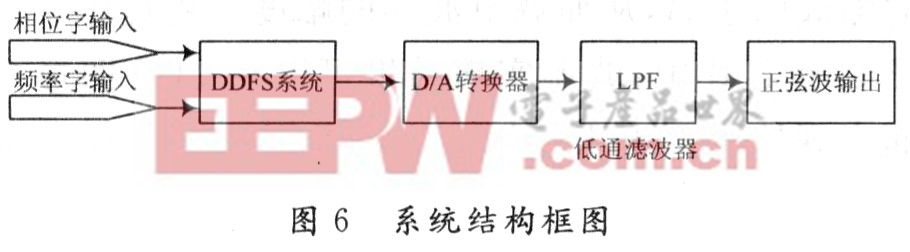

直接数字频率合成(DDFS)电路由系统时钟、相位累加器、频率累加器、波形查找表、D/A转换器和信号调理电路构成。DDFS的工作原理是在每个时钟周期,用频率累加器以输入频率字FW为步进进行自增累加,累加结果的高位送相位累加器,并与输入的相位字PW进行累加,相位累加的输出作为波形查找表的地址,从查找表中读出相应的数据送给D/A转换器,最后经过低通滤波器、后级放大等信号调理电路,以形成模拟量波形输出。图6给出系统结构框图。

DDFS的频率输出公式:

式中:N为相位累加器的位宽;M为频率字位宽;Fclk为系统时钟信号。

DDFS通过数控振荡器产生频率、相位可控的正弦波。其优点体现在无需相位反馈控制,频率建立及频率切换较快,可编程且全数字化,控制灵活方便,输出相位连续。如果在相位累加器的位数N足够大时,理论上可以获得很高的分辨精度,应用DDFS还可以产生其他多种调制信号,因此具有极高的性价比。

2.2 硬件模块设计与仿真

利用DSP BuiIder进行DSP模块设计是SOPC技术的一个组成部分。关键设计过程在Matlab的图形仿真环境Simulink中进行,用图形方式调用DSP Builder和其他Simulink库中,图形模块,构成系统级设计模块,如图7所示。

评论