采用FPGA协处理的无线子系统

Xilinx致力于开发行业领先的工具和体系,能够在比HDL工具(如MATLAB模型和C代码)所能提供的更高的抽象层上实现高效的FPGA解决方案。利用Xilinx专门用于DSP的系统生成开发工具和AccelDSP综合工具,可以尽可能无缝实现从算法到硅片的链接。

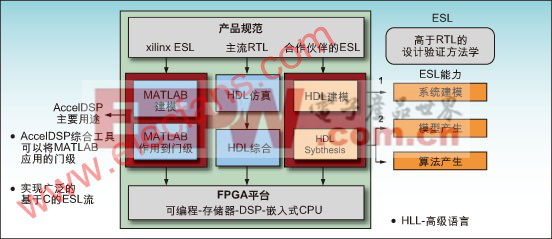

目前有一个日益重要的工具提供商团队,其产品通过C/C++到逻辑门的设计流程把开发提升到电子系统级(ESL)。ESL设计工具的目的是提供一种完备的系统级方法,以便生成和集成硬件加速功能以及控制这些功能的处理器的控制代码。

没有哪一种高级语言或软件工具能适合当今复杂系统中所见的所有不同单元。语言和设计流程的选择取决于客户,有时取决于具体的工程师。因此,Xilinx开发了一套齐全的集成功能,以满足客户需求并提供最佳设计环境(见图3)。

图3:系统级到 FPGA 设计流程

本文小结

另外,Xilinx正在斥巨资提供一套功能广泛的高价值IP、电路板和参考设计,以涵盖射频卡和基带应用中的许多关键部分,其中包括FFT/iFFT、调制、数字上下变频和波峰系数的降低电路等。

这一重点举措的一个例子是开发针对特定无线标准和FPGA架构优化的行业领先的高性能FEC功能,如Turbo编码器和解码器。正如我们在分析3GLTE延迟和Turbo解码器流量要求时所示,FEC功能的硬件加速及其对系统架构的作用在现代无线设备设计中是日渐紧要的当务之需。

虽然一些专家级DSP处理器陆续以嵌入式模块的形式集成这类功能,但是,从制订出符合新无线标准的FEC功能参数到形成嵌入式加速模块出现在硅片中,通常需要好几个月。一旦实现了嵌入,也还会有遗留的难题,偶尔还会有嵌入式模块中的功能并非都能按要求工作的局面出现。同时,标准演化迅速,现标准中不时纳入一些固定嵌入式模块不能支持的新要求。

评论