IIS接口的FPGA实现

如图1所示,FPGA负责连接S3C4510B和UDA1341TS,需要实现S3C4510B总线接口、IIS总线和L3接口等。采用模块化设计思想,划分几个功能相对独立的模块,并将各个功能模块封装成元件(Component),分别设计、仿真、测试、验证各元件,最后在顶层调用各元件,并将元件信号与实际输入输出信号关联,实现整体功能。实际实现了4个元件,如图2所示。

图2中,元件ARM_Interface负责实现与S3C4510B接口,主要是实现几个可以映射成存储器的地址单元,并提供这些单元与其他元件的接口。其中左右声道单元为16位,在内部分别与2个FIFO相连接,以便音频数据以选定的速率回放;IIS_out元件负责产生IIS总线或MSB对齐模式时序;L3_3B_Mod元件实现UDA1341TS数据传输模式中的DATA0扩展地址模式,共需传输3个字节;L3_2B_Mod元件则负责UDA1341TS其余的操作模式,只需传输2字节,即1字节地址和1字节数据。采用这种元件模块设计的方法主要考虑到FPGA容易实现并行操作,但对复杂条件操作和逻辑判断则不如处理器编程实现方便。因此并行实现多个元件,再由简单逻辑和条件及输入参数控制选定的元件工作,以实现需要的功能,这是FPGA设计的主要思想。

2.1 嵌入式处理器接口实现

此模块主要负责处理与嵌入式系统的数据传输接口。主要输入信号包括全局时钟GCLK、片选信号nCS、写信号nWBE0、读信号nOE以及地址信号ADDR[4..0],其中地址信号确定相对于片选地址的偏移地址,5位地址信号最多可寻址32个16位地址单元。所有总线数据操作与全局时钟同步。根据需要,实际设计实现了7个寄存器,分别是DATA0直接地址寄存器、DATA0扩展地址寄存器、DATA1寄存器、STATUS寄存器、左声道音频数据缓存器、右声道音频数据缓存器、FPGA控制寄存器,它们的偏移地址分别是0x00100、0x00110、0x01000、0x10100、0x00000、0x00010、0x01100。上述寄存器中,只有左右声道音频数据缓存器为16位,其余均为8位,因此只能实现不超过16位的IIS总线和MSB对齐模式。

测试本元件时,首先应测试单元的读写特性,通过ARM仿真器直接对编程单元进行读写即可验证扩展的正确性。对于内建16x8的FIFO的左右声道数据缓存器,可以通过读写多次测试其满空状态,并通过1个接在FPGA的I/O口线上的LED直接观察。测试无误后,该元件便可使用。

2.2 IIS总线实现

IIS总线通过IIS_out元件来实现,其接口信号如图3所示。输入信号是ARM_Interface提供的左右声道音频数据,输出信号是IIS总线要求的3个串行信号,即bclk、sync和dout,分别与SCK、WS和SD对应,这3个信号通过FPGA的I/O口线与UDA1341的BCK、WS以及DATAI与DATAO信号线相连。IIS 格式的信号无论有多少位有效数据,数据的最高位(MSB)总是被最先传输,在WS 变化后的第2 个SCK脉冲处,因此最高位拥有固定的位置,而最低位的位置则依赖于数据的有效位数。实际设计的数据有效位是16位,低于16位数据时高位填充‘0’,处理器将数据以16位方式写入左右声道音频数据缓存器时,自动进行高位填充。

实现IIS总线时序时,关键是要正确处理各种时钟信号之间以及生成的IIS总线3个信号之间的时序关系。要依据音频信号的采样速率选择FPGA系统时钟和UDA1341时钟选项,同时要合理使用计数器并正确读取左右声道音频数据缓存器,最终实现音频数据通过IIS总线的正确传输。

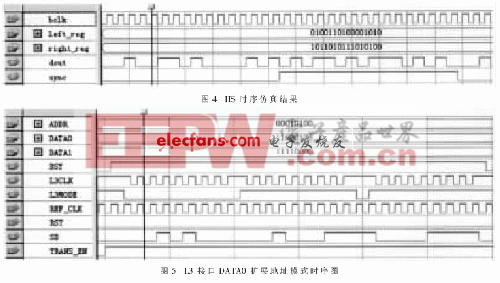

设计实现的IIS时序仿真图如图4所示。

图4显示的是IIS_out元件将左右声道音频数据缓存器内2个16位数据由IIS总线输出的时序仿真结果。bclk信号的上升沿数据dout稳定有效,在bclk为低电平时dout才变化。当左右声道控制信号sync为低电平时,传输左声道数据‘0111011101110111’;当sync为高电平时,传输右声道数据‘1010101010101010’。从仿真波形可知,每声道数据反映在dout波形上是从sync电平变化后的第2个bclk周期开始的。

图2所示的最高位对齐模式与IIS使用相同的信号,很容易在IIS总线的基础上修改实现。实际实现的最高位对齐模式仿真时序正确,在此不再详述。

评论