基于DSP的高阶COSTAS锁相环的设计

3.1 SIN/COS函数的查表算法

为了提高算法的实现效率,介绍运行时计算的时间开销,应尽可能把一些运行时计算的参数做成查找表或常数数值。这不仅适用于一些比较规整的参数表,对于一些并不规整的运行时的计算,例如上下变频和VCO中,用到与载波相乘的SIN/COS的计算,可以采用写成数组,用查表来实现。

3.2 运算的流水处理

DSP的CPU多采用流水线结构。DSP的大多数指令为单周期指令,而跳转类指令却通常要耗费较多的机器周期。可以将多重循环拆开,减少对外层循环次数进行控制转移的时间,充分利用优化器构成的流水线。

3.3 CIC梳状滤波器的使用

利用CIC滤波器代替低通滤波器,达到减少定点乘法和加法运算的目的,解决了单片C6416资源不足的问题。例如:本文中载波速率为4800kHz,采样率为230.4kHz,鉴相器输出的高频频率为9600kHz,采用48阶CIC可以将9600kHz的频率分量滤掉。由于在 的位置,因此滤除效果非常好,远大于 。CIC滤波器每项系数都是1,利用加法运算可以实现需要大量乘法和加法运算的功能,减少对DSP片内资源的使用。

3.4数据传输的EDMA方式

在调制解调过程中,DSP和外部之间存在大量数据的交换,这部分的优化工作影响系统性能。C64x支持EDMA,EDMA是增强型DMA,是一种在没有CPU介入情况下的访问存储器的方式,即由EDMA控制器控制数据在L2内存/缓存和片内集成外设及片外设备之间的传输,而同时CPU可以并行的执行其它指令。EDMA是一种有效的数据传输方式,可以有效的减少EMIF在CPU下操作需要的资源。

具体实现方法如下:在片内数据存储区定BUF的长度,并一分为二,可设为BUF1和BUF2。在EMDA里BUF1和BUF2都是等存储大小的。在数据帧同步信号的上升沿,DSP以EDMA的方式从外部读一帧的数据到BUF1;同时BUF2内的数据进行MPSK的解调算法。同理,在下一个数据帧同步信号的上升沿,DSP以EDMA的方式从外部读另一帧的数据到BUF1 。BUF1读满后,DSP对BUF1内的数据进行MPSK的解调算法,同时BUF2进行数据的读操作,实现EDMA的乒乓处理。

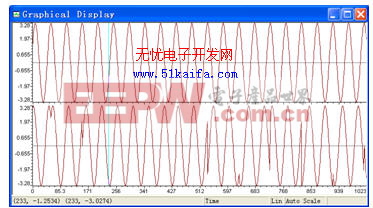

本文选取8PSK的符号速率为2400kbps,载波速率为4800kHz,采样率为230.4kHz。图2所示的两路信号分别是利用CCS开发工具的观察窗口观察到的,提取的同频同相的载波信号和8PSK的调制信号。

图3 恢复的载波信号(上)和接收到的基带信号(下)

图4 8PSK接收端解调前星座图(AWGN信道,SNR=17dB)

5. 结束语

本文主要介绍了一种新型的适用于MPSK载波提取的高阶COSTAS环路,能满足MPSK相干解调的需要,且便于DSP实现。针对COSTAS环算法的DSP实时实现问题,进行了详细的讨论。最后,针对一个具有较高数据速率8PSK调制解调实例,在单片C6416上完成了基于高阶COSTAS环的载波同步及相干解调,并给出了通过CCS工具观察到的DSP实现结果,证明高阶COSTAS锁相环具有较好的载波同步性能。

低通滤波器相关文章:低通滤波器原理

鉴相器相关文章:鉴相器原理 锁相环相关文章:锁相环原理

评论