一种FPGA能耗优化的方法设计

实时的电源分析和优化

在不影响产品设计的前提下,使能耗达到FPGA设计的电源的预算要求需要电源分析工具利用一切可能得到的帮助。需要在开发过程中提供很多的信息,使得在原型阶段之前就完成最主要的产品设计决定。

从最终产品的角度来看,FPGA的能耗就只是问题的一部分了。电源分析和测试需要扩展到外设电路和支持设备,这样这些部分才能在开发时不断修改,以达到能耗优化的目的。

一种实时的方法可以让FPGA设计达到设计的要求并在最后日期之前完成优化工作。在开始的时候,设想FPGA开发板拥有通过一系列的感应器实时进行电源监控的能力,并将获得的数据反馈回设计软件(图1)。

这样,电源的实时情况就可以被监视,图表化并被记录下来。因为节电模式包括重新编程产生的高峰所产生的能耗可以被精确估计,嵌入式硬件和软件的选择就可以被广泛的开发了。关于能耗的预测则进入了量化的阶段。

下一步就是让最终产品系统,包括开发板和设计软件独立于FGPA厂商和器件。这需要开发板具有可插拔和容易交换的FPGA卡板,而且每一个变化的数据都会回复到设计软件。之后设计软件可以根据系统驱动结构文件来支持很多不同的FPGA设备,用预先验证并整合的IP组合来支持所有这些兼容性。

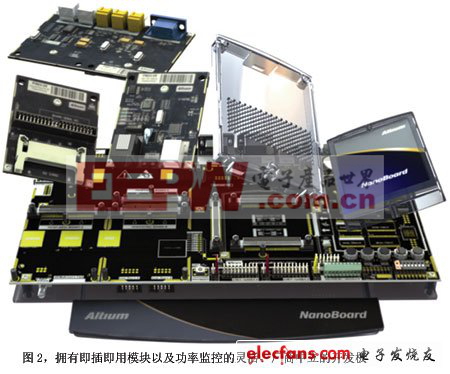

如果软件系统还包括嵌入式设计的高度抽象捕捉功能,例如原理图或者图形流程的界面,就可以使和嵌入式的互动变得更为容易。嵌入式设计可以被容易实现或者被修改,当FPGA设计被改变后电源能耗的变化可以被高级开发板即时的记录。该开发板还可以涵盖拥有“智能电源探测器”的子板,记录所有的硬件实施,以便从功能和电源有效性的角度进行分析(图2)。

更进一步来说,如果开发板忠实反映产品开发选择或者甚至目标产品就是开发板,从开发到原型的时间就会大幅的缩短,对于能耗分析预测工具的要求也就不是那么多了。这样,设计的开发板就可以代替原型,并且在产品开发的过程中精确的执行能耗控制。

有了这样的方法,你就可以有效地开发最终产品的设计,并可以应用在适合的即买即用或专门定制的板子上。这样的系统不再需要依靠传统的能耗预测工具提供精确的数值,相反可以让用户可以很方便的在不同的FPGA器件上迁移自己的设计,并迅速探索将嵌入式设计的选择。

为未来做准备

在目前的设计里激发FPGA的所有特性,特别是在那些电池供电的设备中,意味着对FPGA能耗的完全理解和控制。

FPGA厂商为了迎合市场对低功耗的需求,推出了基于flash的非波动设备,有效能耗架构和高级节电模式。但是不管怎么样,基于FPGA的设计总会在能耗的有效性和功能之间有所取舍。所以选择一个合适的工具来平衡这样的取舍就显得至关重要。

为了今天和明天的设计,关键是要解决如何有效的通过真实快速的原型建立来解决能耗有效性的平衡问题。用户不能仅仅依靠能耗的预测和分析工具,而要引入先进的设计系统并在硬件上进行实时开发。这样工程师就可以充分的探索创新的设计来最大限度的激发FPGA的所有特性,并用于开发新一代的节能产品。

评论