基于ARM和FPGA的时间同步仪控制单元设计

2.4 以太网接口电路设计

网络传输模块使用Devicom公司研发的一款快速以太网控制芯片DM9000A,其内部集成了10/100 MB物理层接口,支持8/16位数据总线,内置16 kB的SRAM,用于收发缓冲。

S3C2440A内部没有集成专用的以太网控制器,所以需要外挂一个以太网控制器。系统采用DM9000A作为以太网的物理层接口。S3C2440A与DM9000A的连接如图所示。S3C2440A的数据总线LDATA15~LDATA0与DM9000A的SD15~SD0连接;地址线LADDR3与DM9000A的CMD连接;片选DM_CS与DM9000A的CS连接;DM_IOR/DM_IOW分别与DM9000A的IOR/IOW连接;EINT8与DM9000A的INT连接。以太网控制器DM9000A的工作地址为0X30 0,因为S3C2440A的地址线LADDR3与DM9000A的CMD连接,所以对其进行操作时分为以0X300作为地址端口和0X304作为数据端口。

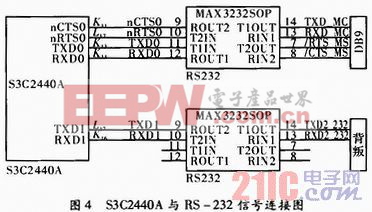

2.5 RS232接口电路设计

S3C2440A集成了3个串口UART0、1、2,文中用到UART0,UART1,其中UART0作为标准串口通信,与宿主机相连用于系统调试、超级终端控制和文件收发;UART1与单片机ATMEGA128连接,其作用是传递导航电文和状态参数给GSG单板。图4为S3C2440A与RS-232信号连接图,其中上方的MAX3232SOP作为UART0使用,下方的MAX3232SOP作为UART1使用。本文引用地址:http://www.eepw.com.cn/article/148830.htm

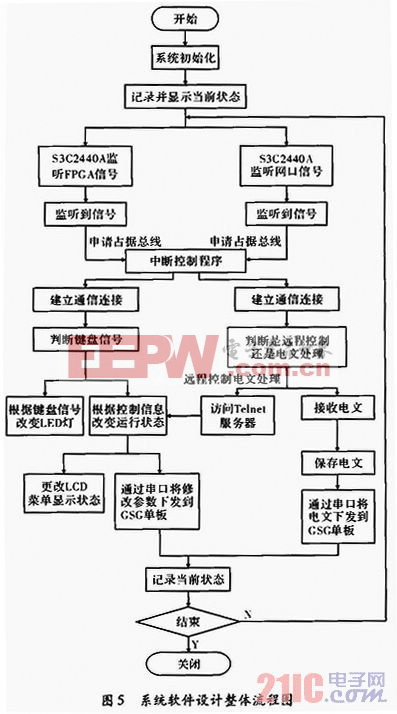

3 系统软件设计

系统的软件部分是在Linux操作系统下实现的。结合控制系统的功能分为人机交互、参数设定、电文处理、远程控制4个模块,图5为软件设计流程图。

评论