基于OuartusⅡ的电子抢答器设计

本文引用地址:http://www.eepw.com.cn/article/148371.htm

2.4 计分模块的设计

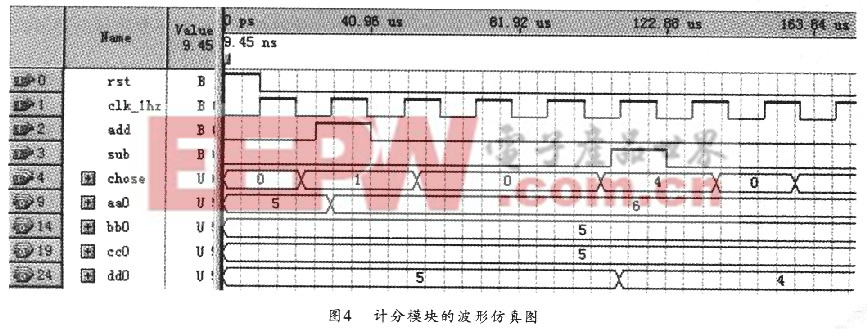

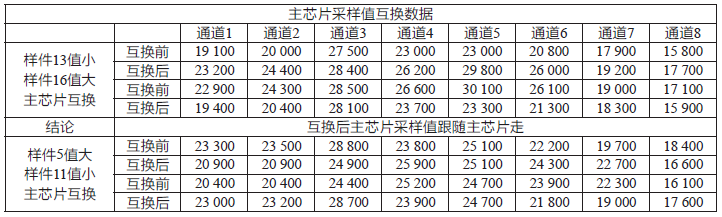

计分模块的主要功能是对抢答成功并答对的组别进行加分操作或对抢答成功但答错的组别进行减分操作,同时通过译码显示电路显示出来。根据以上的功能设计要求,该模块需要将加、减分操作add、sub和系统时钟clk_lhz作为输入信号,而各组别的分数显示作为输出信号aa0[3..0]、 bb0[3..0]、cc0[3..o]、dd0[3..0];为了确定给哪个组别加或减分,需要有一个抢答成功组别的输入信号,可将其设为chose。为了使系统能进入下一轮的抢答,应设置系统复位输入信号rst。其计分模块的仿真模型如图4所示。

通过图4可以看出,当rst=l时,系统进入初始状态,a、b、c、d组的初始分值都为5,当add=1,系统时钟信号clk_lhz的一个上升沿到来时,就给chose当前鉴别的组别“0001”组加1分,当sub=1,系统时钟信号clk_lhz来一个上升沿时,就给chose当前鉴别的组别 “0010”组减1分。

3 电子抢答器的硬件验证

本设计选用杭州康芯电子有限公司生产的GW48EDA系统作为硬件验证系统,同时选用Altera公司的EPlK30TCl44-3作为主控芯片。该主控芯片是一种基于查找表结构的现场可编程逻辑器件,它的基本逻辑单元是可编程的查找表,能够实现组合逻辑运算,并能用可编程寄存器实现时序逻辑运算。设计时,只需要对电子抢答器整体设计中的输入输出引脚作引脚锁定,然后重新编译、下载,就可以进行电子抢答器的硬件验证了。实验表明:本设计能够实现电子抢答器的全部功能。

4 结束语

本文以现场可编程逻辑器件(FPGA)为设计载体,以硬件描述语言(VHDL)为主要表达方式,以QuartusⅡ开发软件和GW48EDA开发系统为设计工具设计了一种具有第一抢答信号鉴别和锁存、计时和计分,并可对提前抢答和超时抢答进行蜂鸣警示等功能的电子抢答器。阐述了电子抢答器的工作原理和软硬件实现方法。并对电子抢答器的各部分模块进行了时序仿真和硬件验证,结果表明,该电路能够实现其所要求的功能。另外,由于FPGA芯片体积小,功耗低,价格便宜,安全可靠,稍加修改就可以改变抢答器的抢答组别数,而且抢答时间设定和成绩组成方式以及维护和升级都比较方便,同时也很容易做成ASIC芯片,因而具有较好的应用前景。

评论