基于CPLD的DSP人机接口模块的设计

本文引用地址:http://www.eepw.com.cn/article/148289.htm

电平转换芯片的选择

由于CPLD为3.3V的器件,而LCD是5V的器件。所以为了CPLD和LCD之间的电平匹配,需要借助电平转换芯片来完成从3.3V到5V之间的相互转换。选择的电平转换芯片是TI公司的SN74LVC4245A芯片,这个芯片的数据传输方向是双向的,在引脚DIR的作用下,既可以实现从3.3v向5v转换,也可以实现从5v向3.3v转换。

为了液晶模块能够正确的工作,液晶需要上电复位。本设计中采用的字体是8×8点,所以在硬件电路设计时将FS引脚拉低。

在硬件设计时,我们需要注意的问题是:

(1)在VDD对地(Vss)间接0.1u左右电容去耦,接10u或20u电容滤波;

(2)模块的复位脚/RST接一个复位电路,而且我们也将/RST与CPLD相连,这样我们也可以利用DSP对其进行复位,使得可以是液晶进行定时刷新,预防一些其他干扰;

(3)在做实验时,FG(铁框地线、不能悬空,暂时与数字地连接。

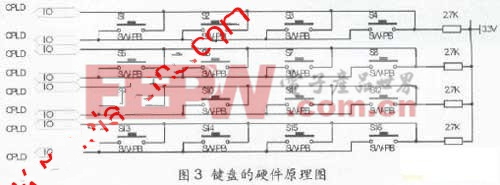

键盘硬件设计

键盘在信号采集系统中是一个很关健的部件,它能向系统输入数据、传送命令等功能,是人工干预系统的主要手段,本系统所用键盘是常用的4×4矩阵式键盘。

16个键盘有0~9数字键,上翻,下翻键,编程键,输入键,擦除键,点号健等。键盘的行线和列线分圳连接CPLD的一个I/O引脚。键盘的行线上有一个2.7k的上拉电阻将行线所连接的CPLD的I/O引脚上拉直高电平。

图3为键盘设计的硬件原理图。

键盘工作原理

按键设置在行、列线空点上,行、列线分别连接到按键开关的两端。行线通过上拉电阻接到3.3v上。平时无按键动作时,行线处于高电平状态,而当有按键按下时,行线的电平状态将由与此行线相连的列线电平决定。列线电平如果为低,则行线电平亦为低,列线电平如果为高,则行线电平亦为高。这一点是识别矩阵键盘按键是否按下的关键所存。由于矩阵键盘中行、列线为多键共用,各按键均影响该键所在行和列的电平。因此各按键彼此将互相影响,所以必须将行、列线信号配合起来并作适当的处理,才能确定闭合键的位置。

结语

本文简单介绍了TI16位控制器DSP与液晶显示模块及键盘模块之间的接口方案.利用了CPLD来进行逻辑转换和控制。提供了一种高速器件和慢速接口直接的连接方法,通过这个接口方案研究,为以后系统的开发提供了一种新的思路。

评论